Memory cont. #

Fragmentation #

The small 2B chunk will never be able to be used, and the sum of all of these small gaps in memory is wasted, called internal fragmentation.

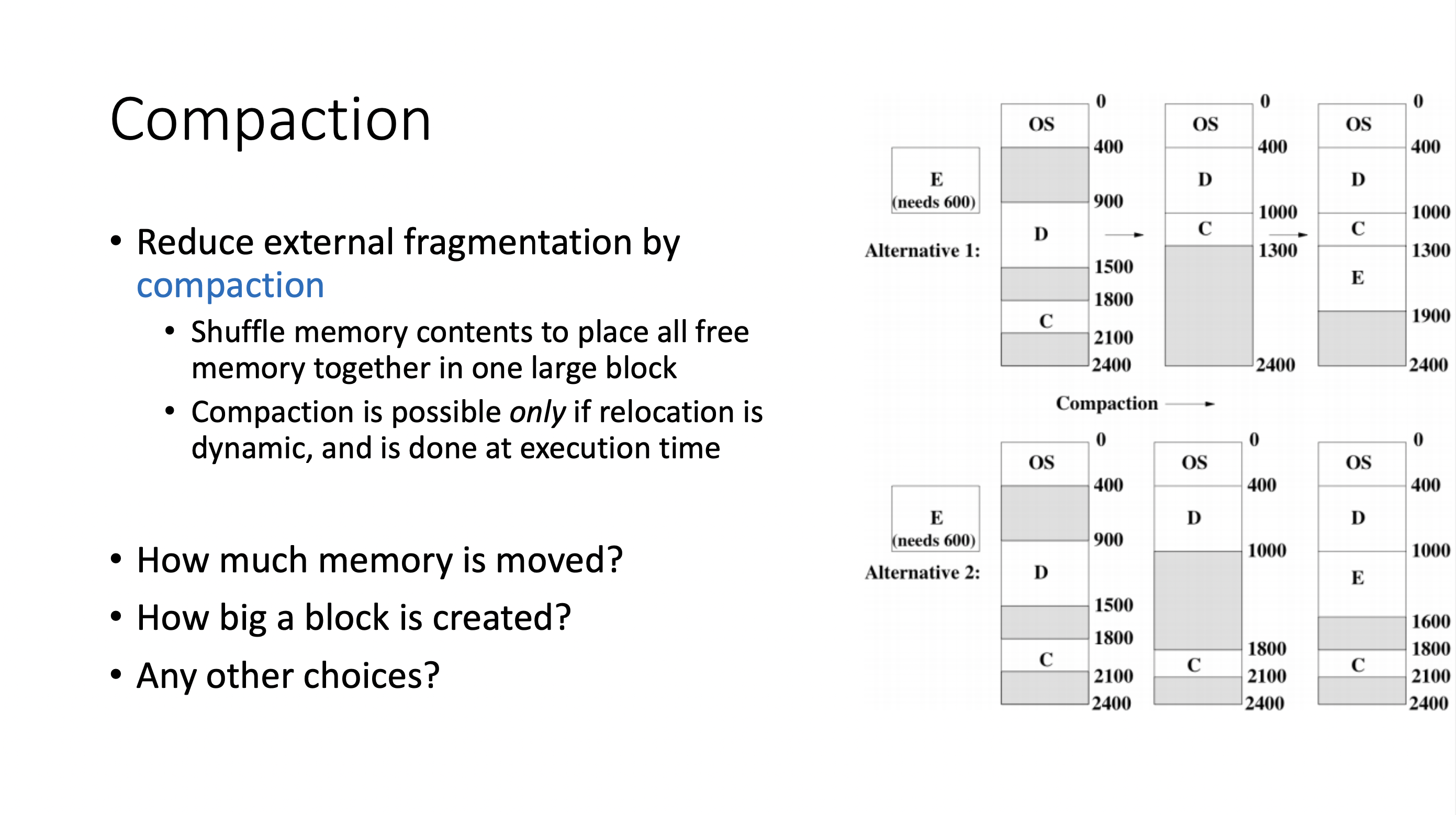

Compaction #

- compaction is expensive to invoke

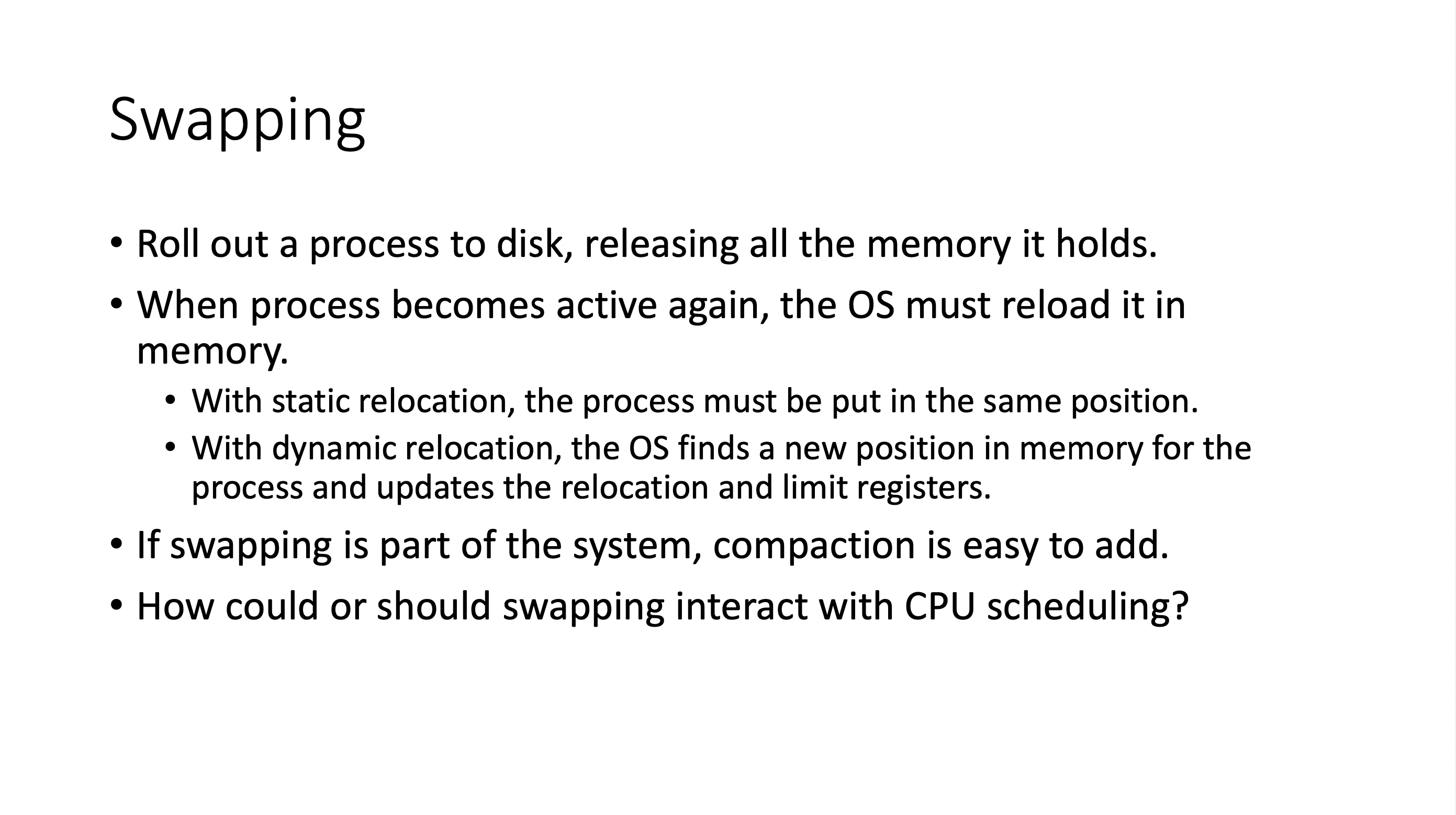

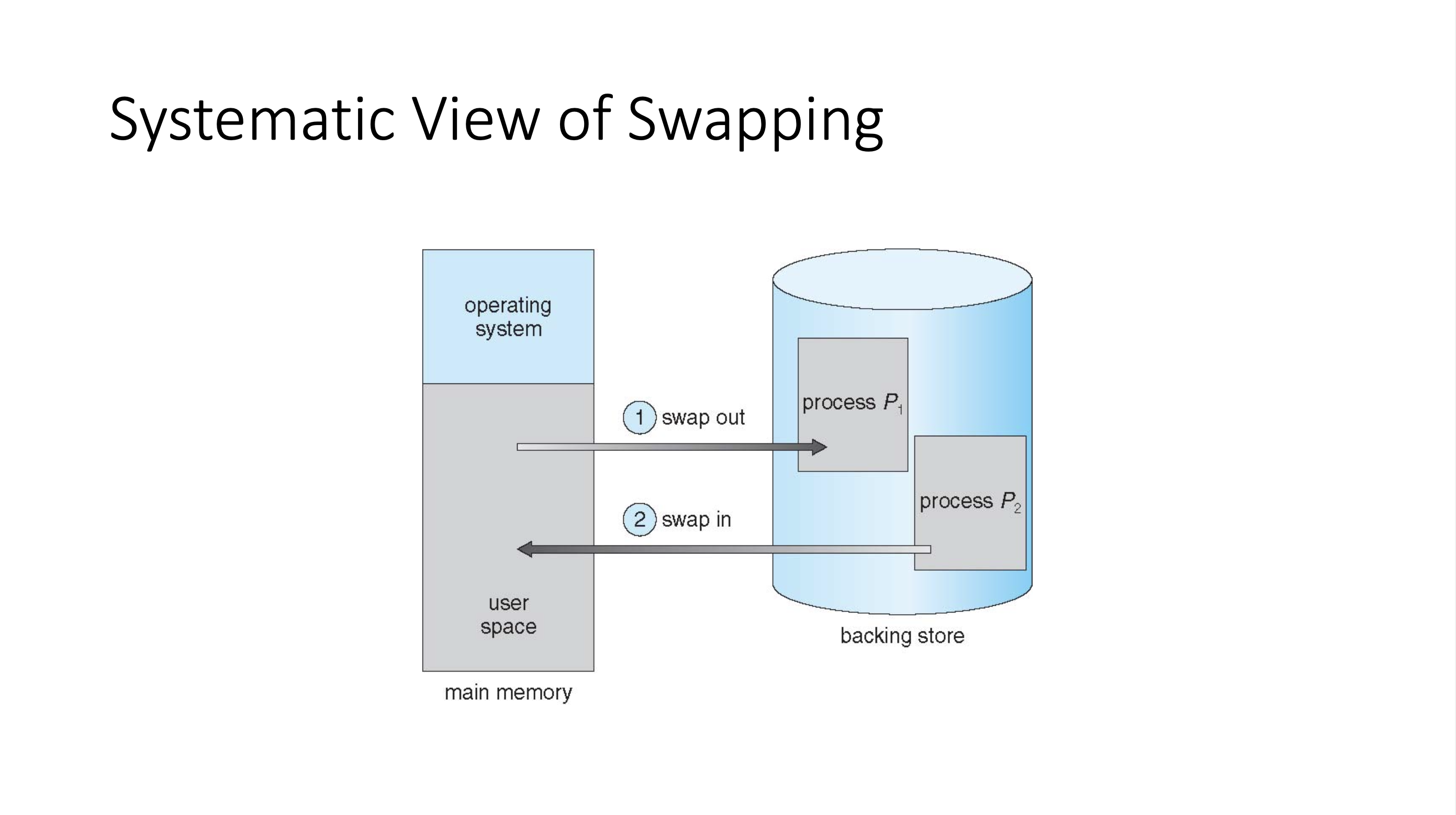

Swapping #

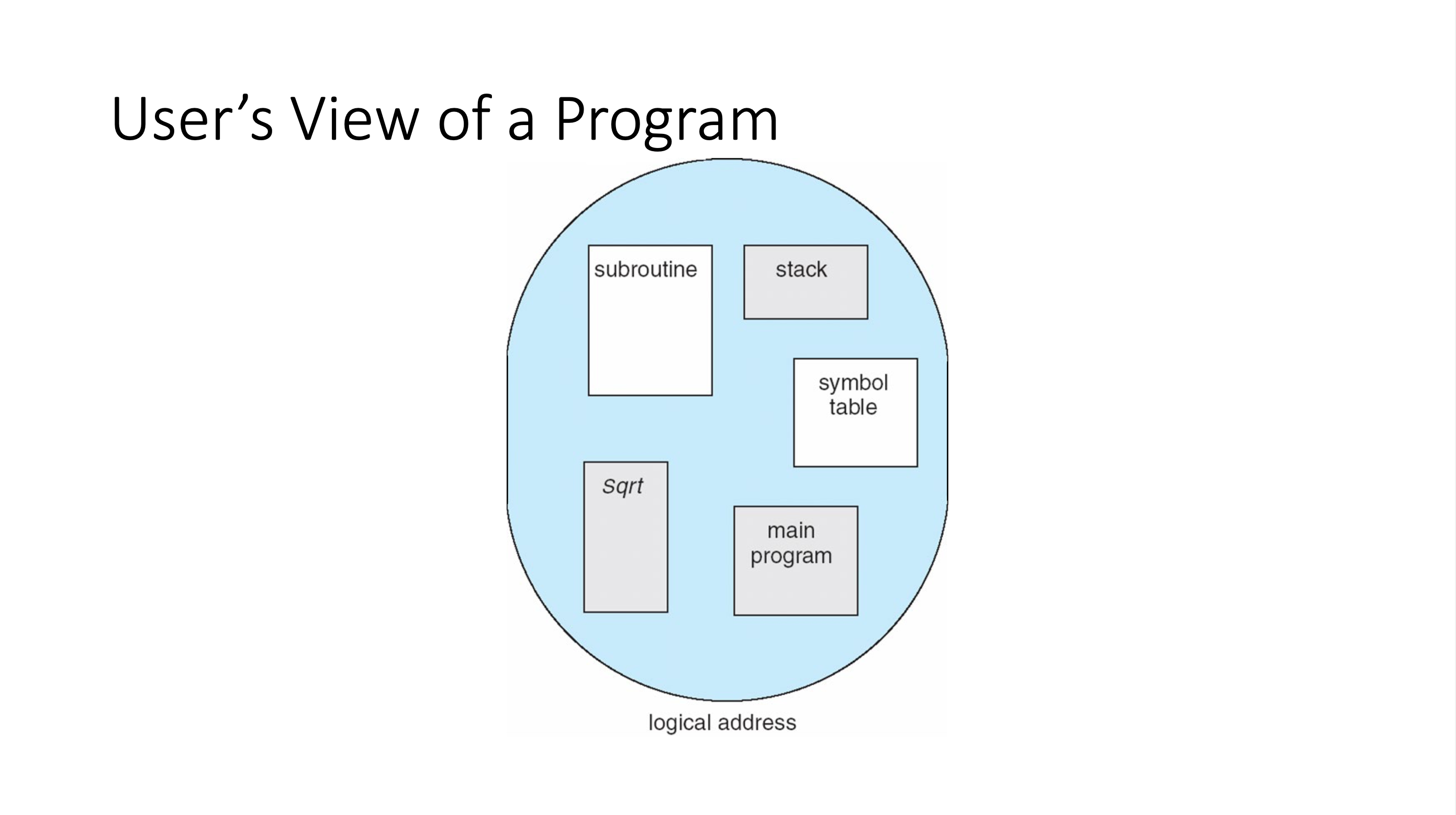

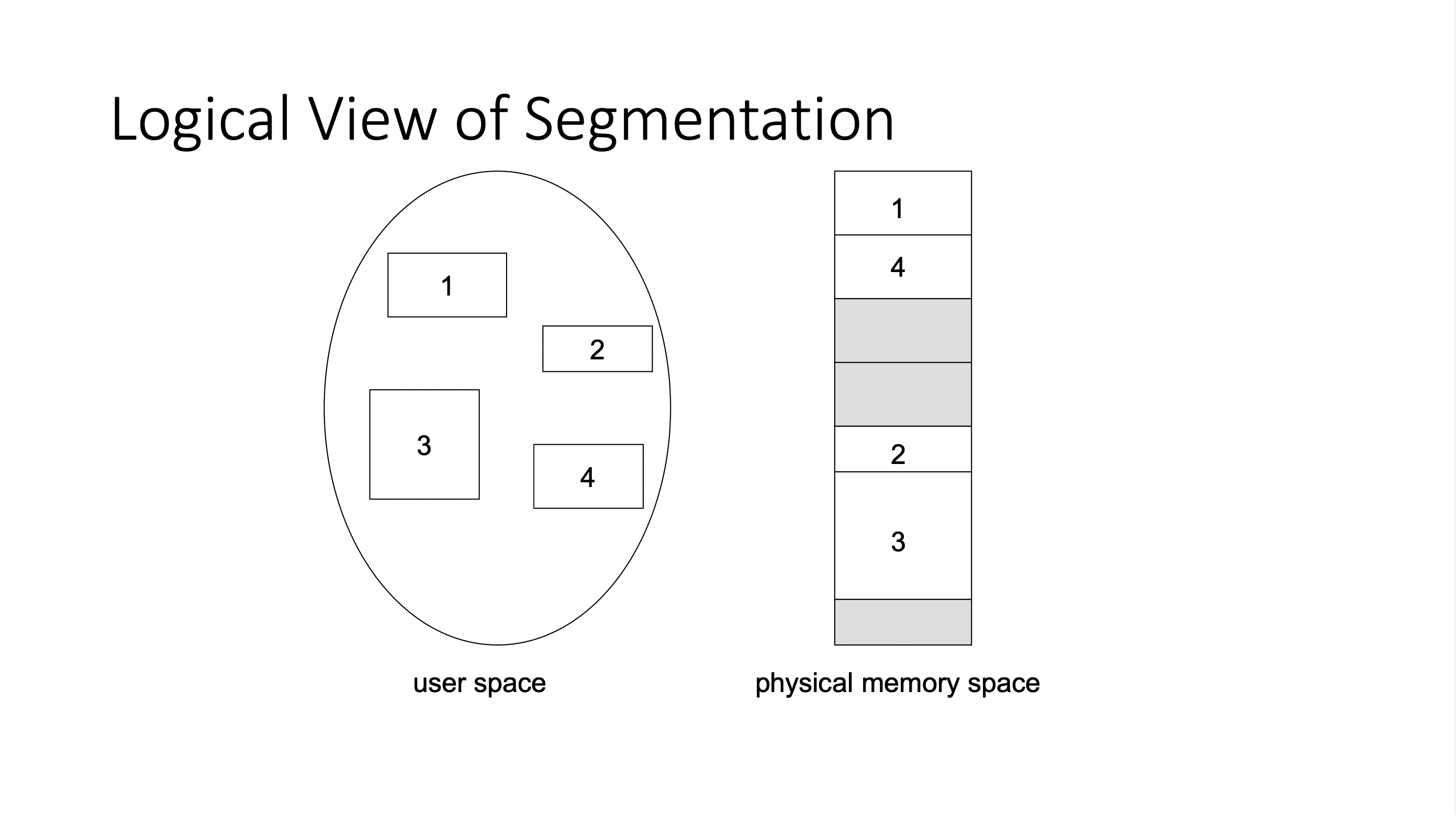

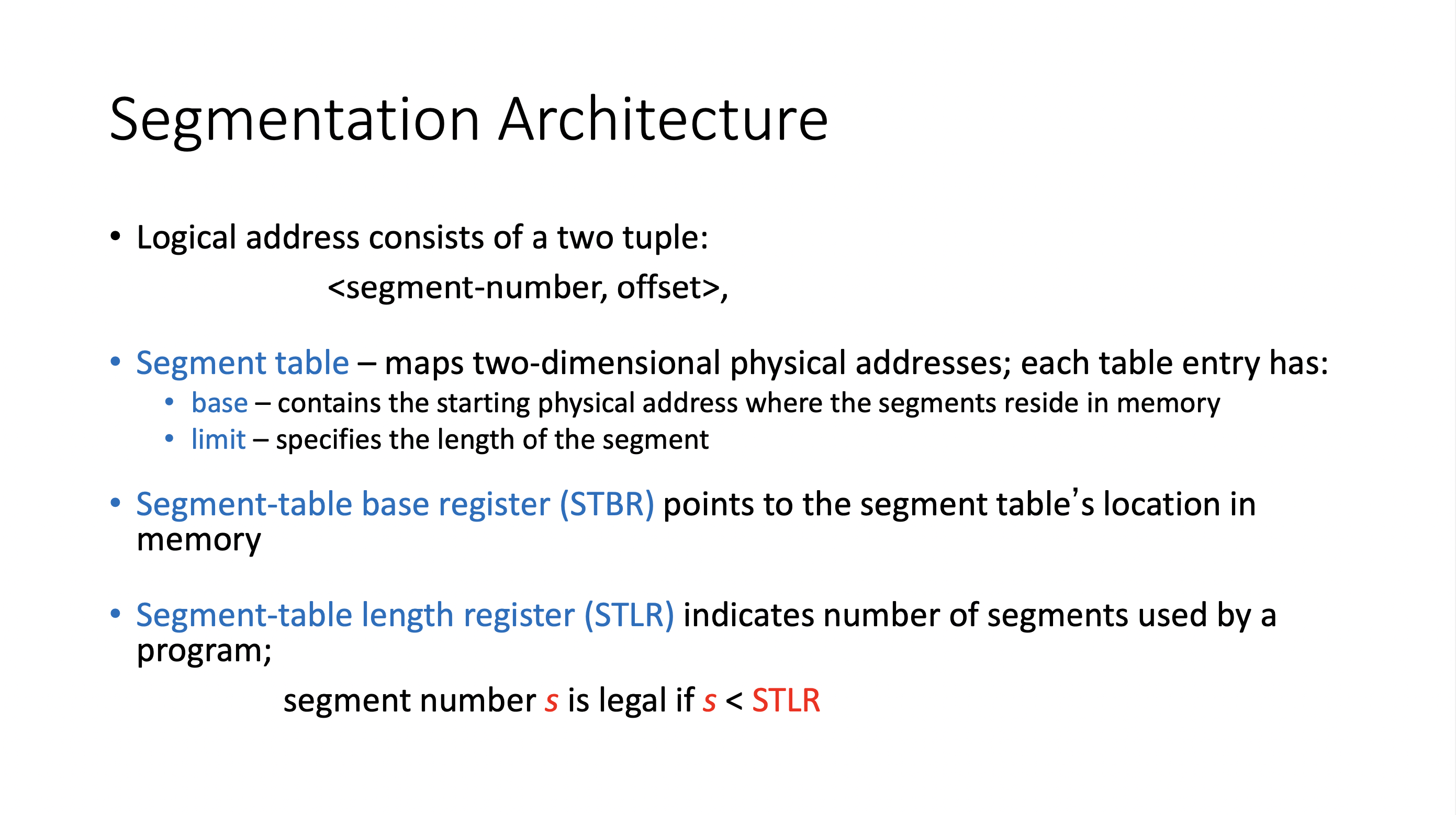

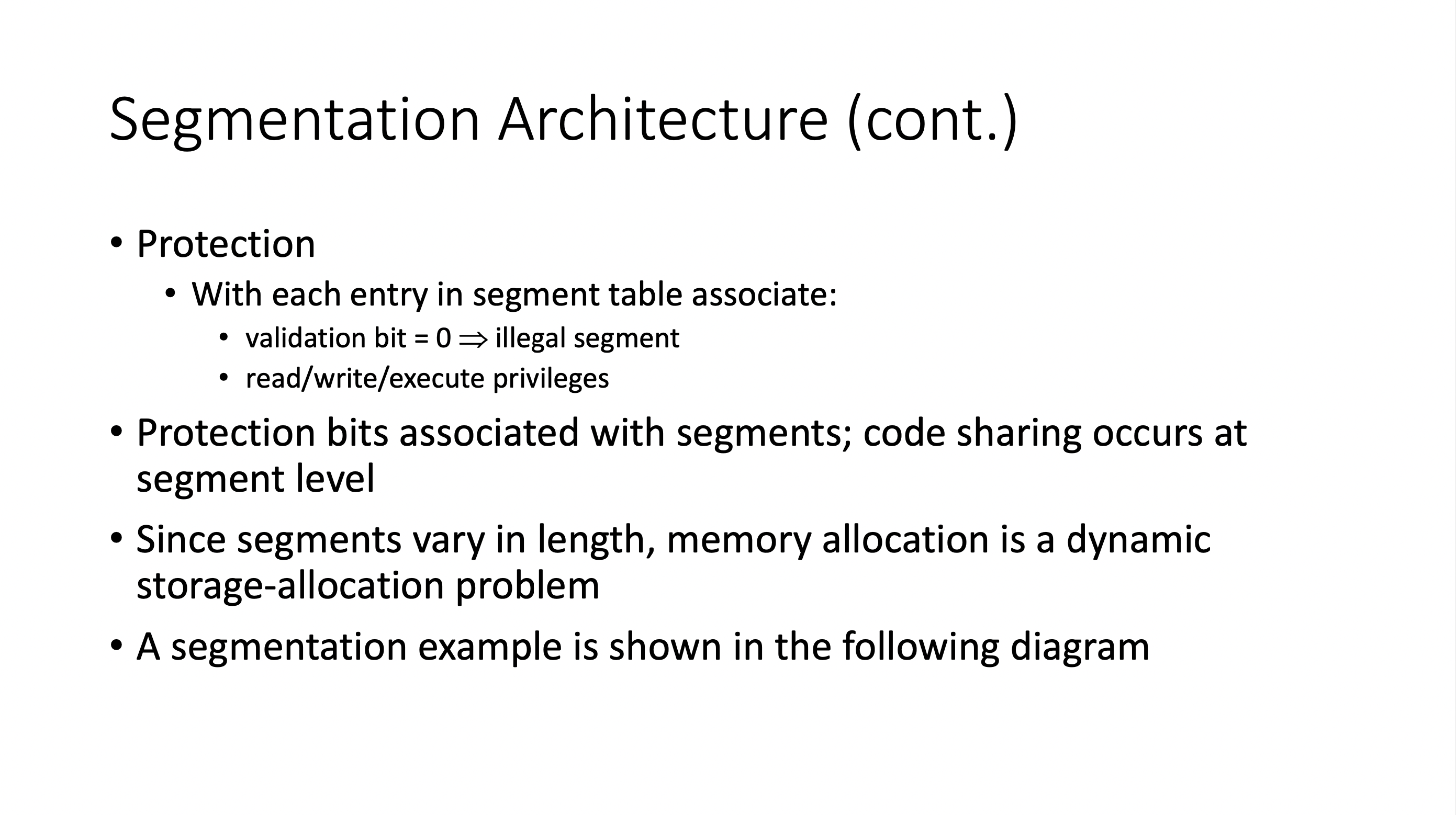

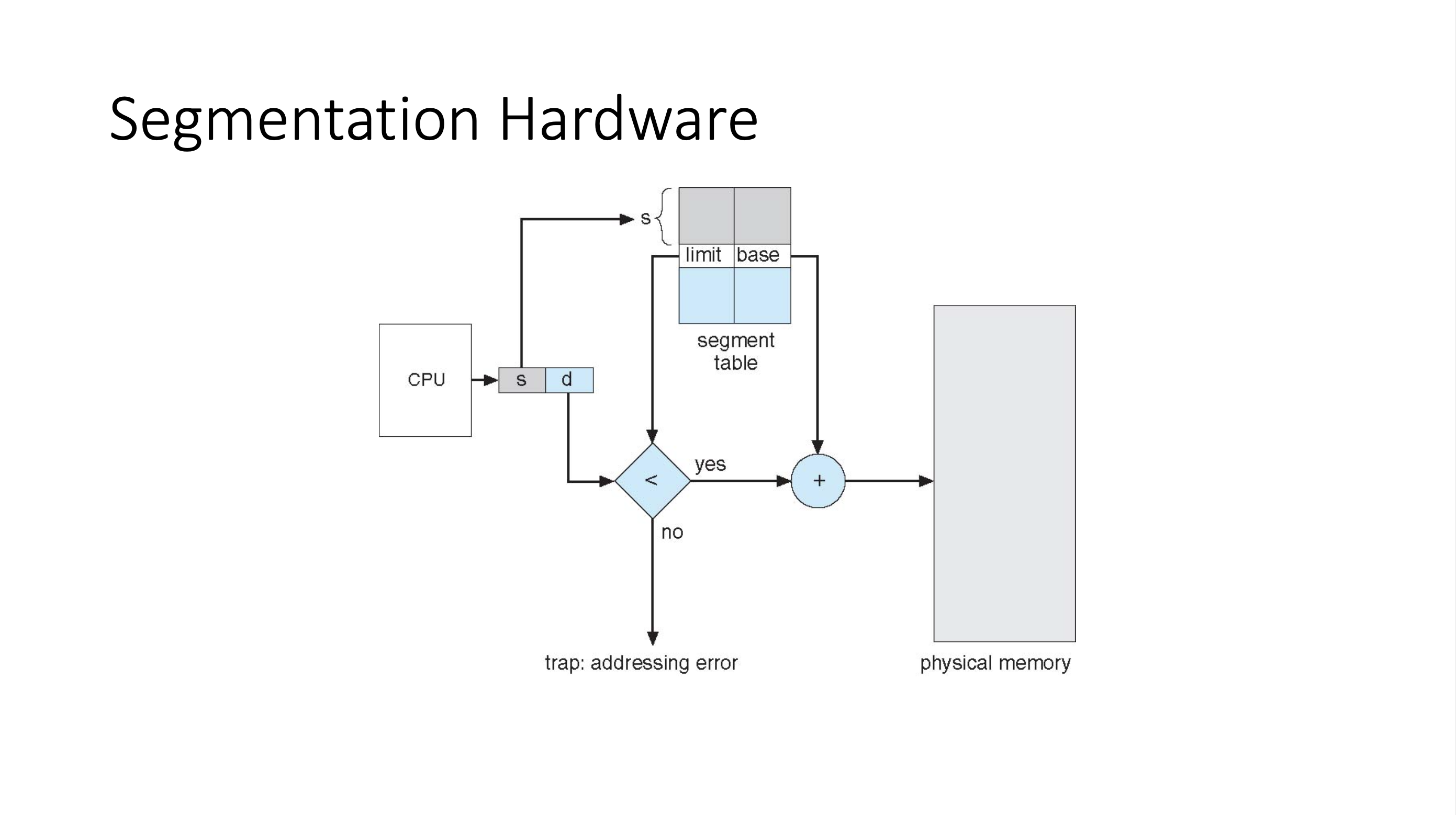

Segmentation #

One of the methods of implementing non-contiguous memory is segmentation.

- an address may be something like

<3, 14>, which represents segment 3 with a 14 byte offset - another table keeps track of the segment’s addresses and lengths

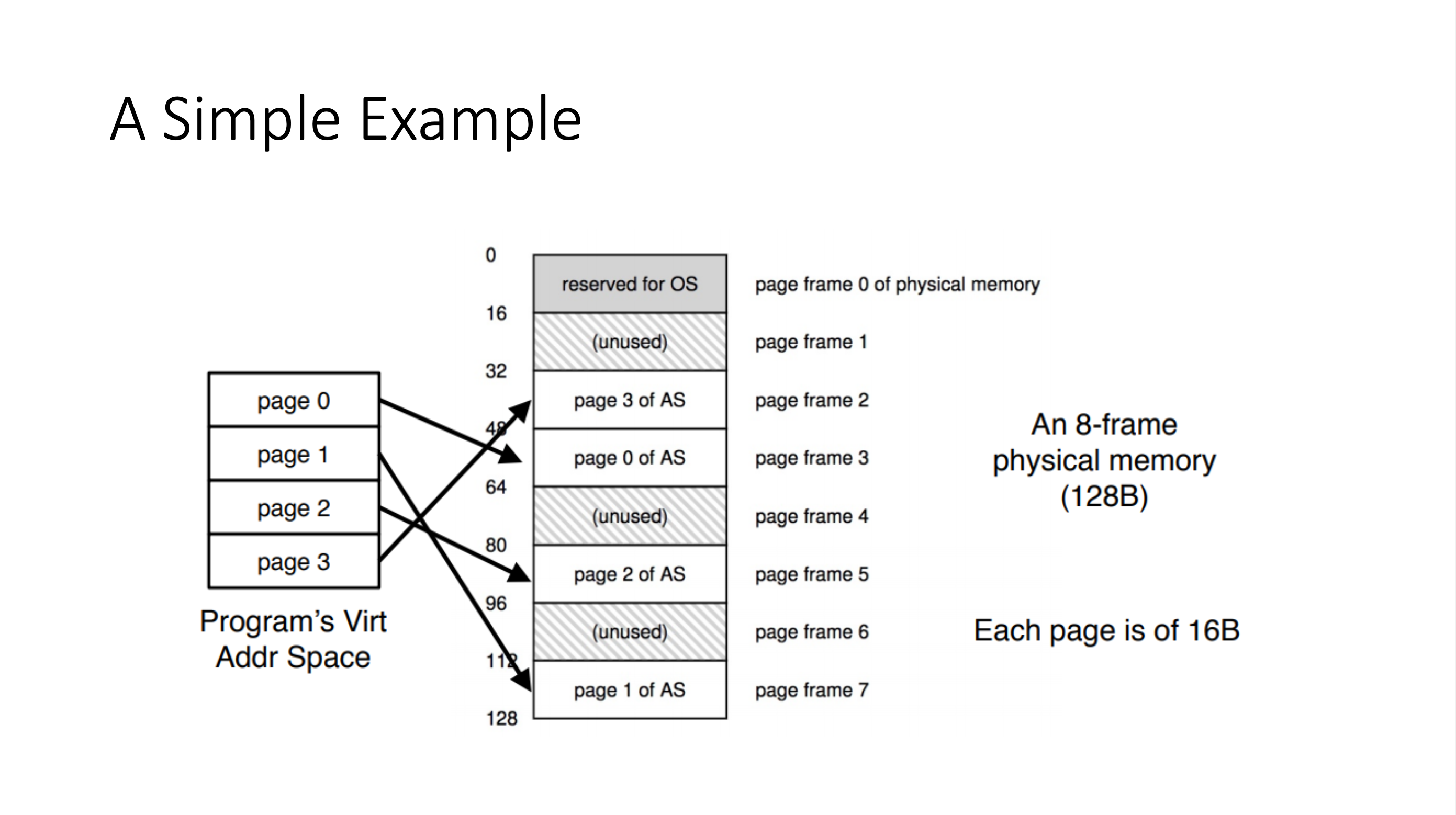

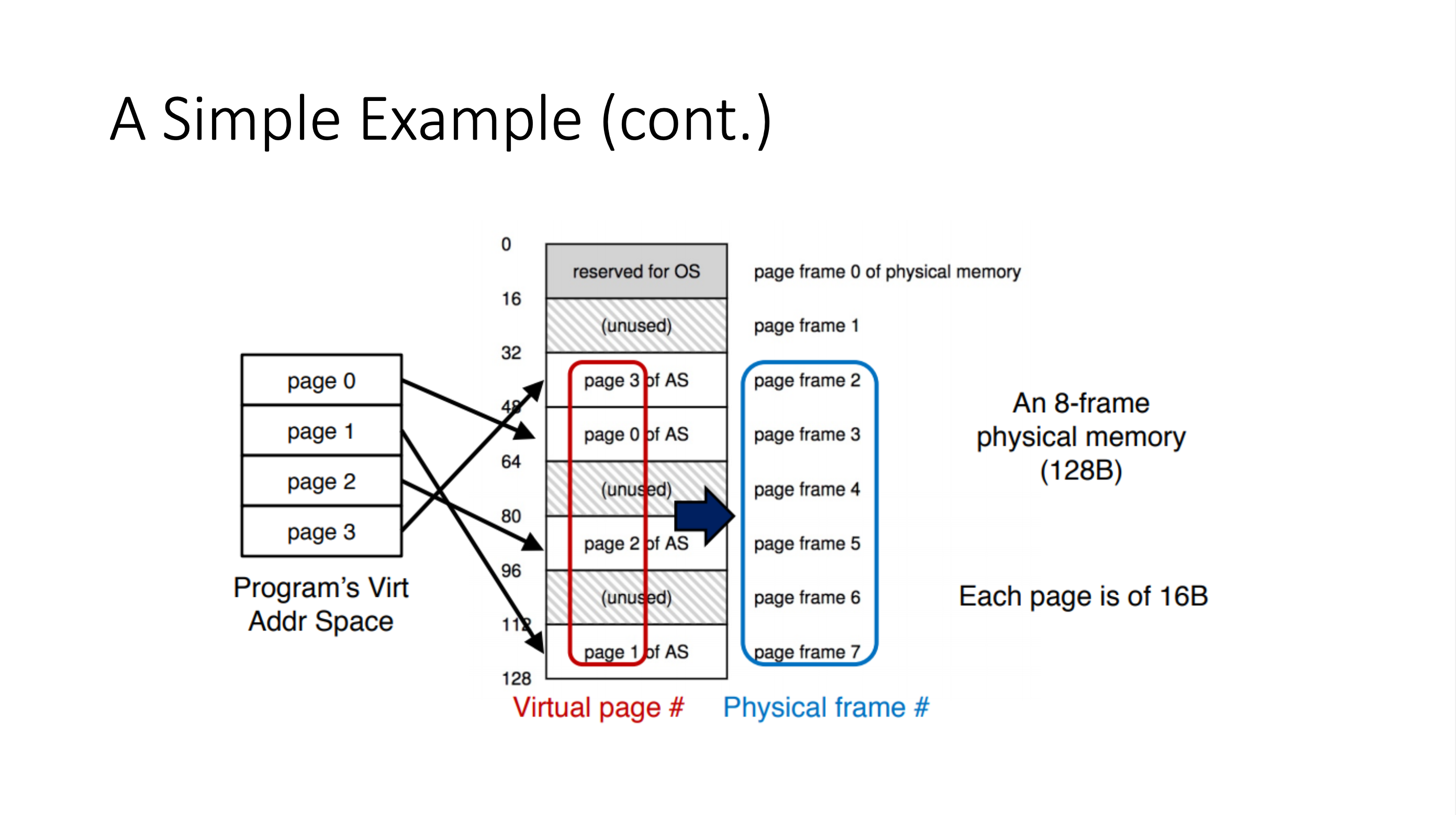

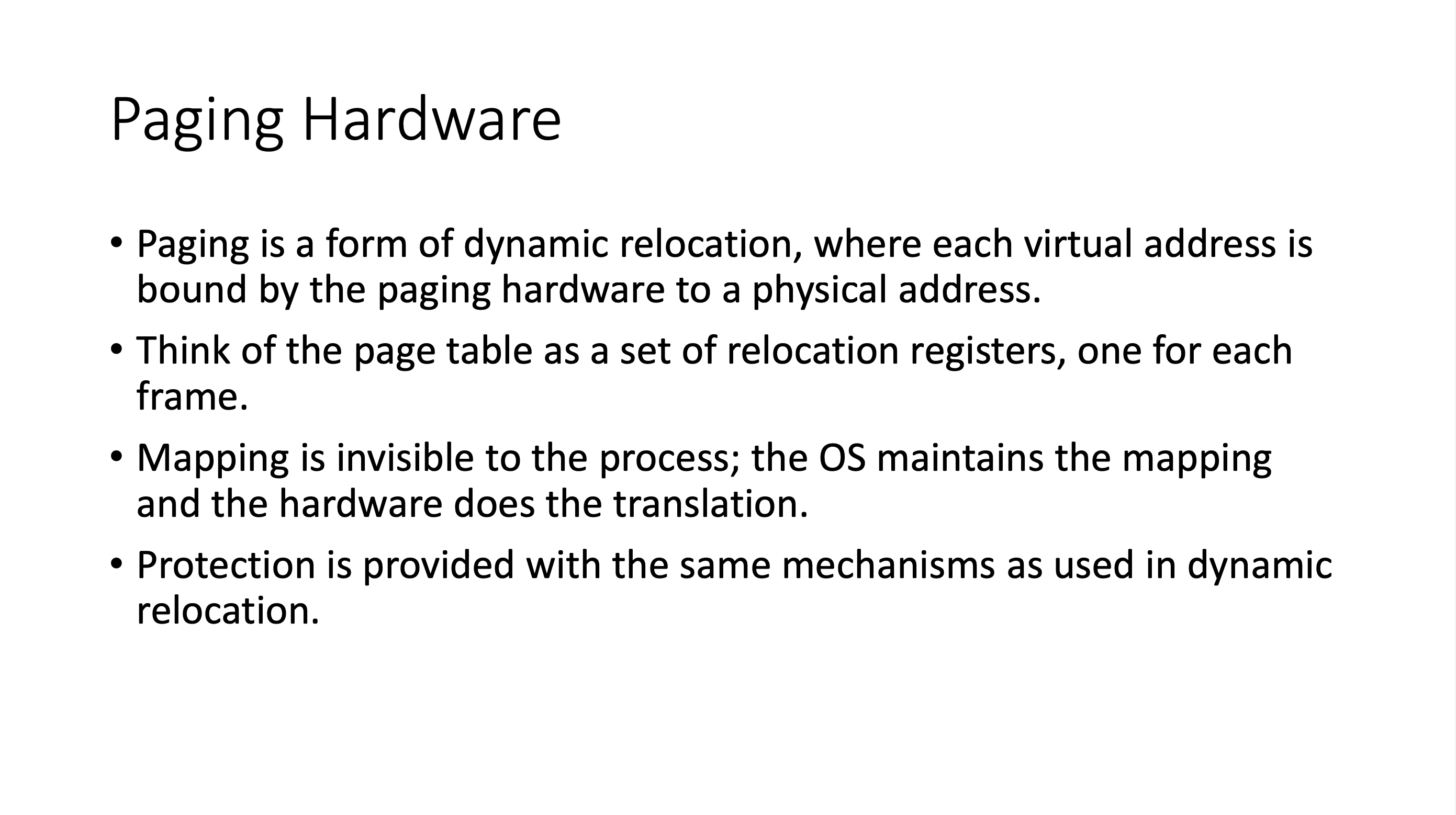

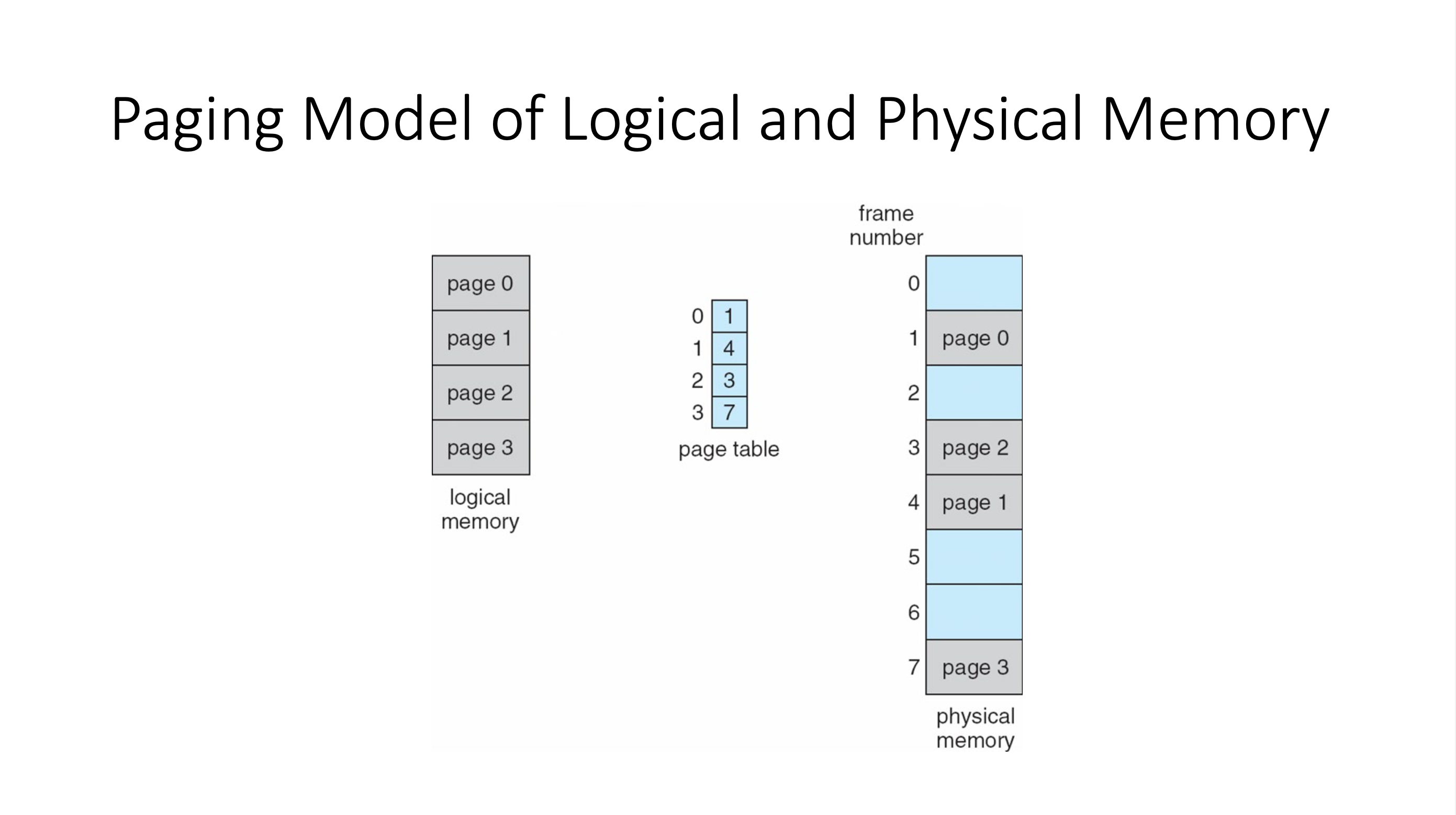

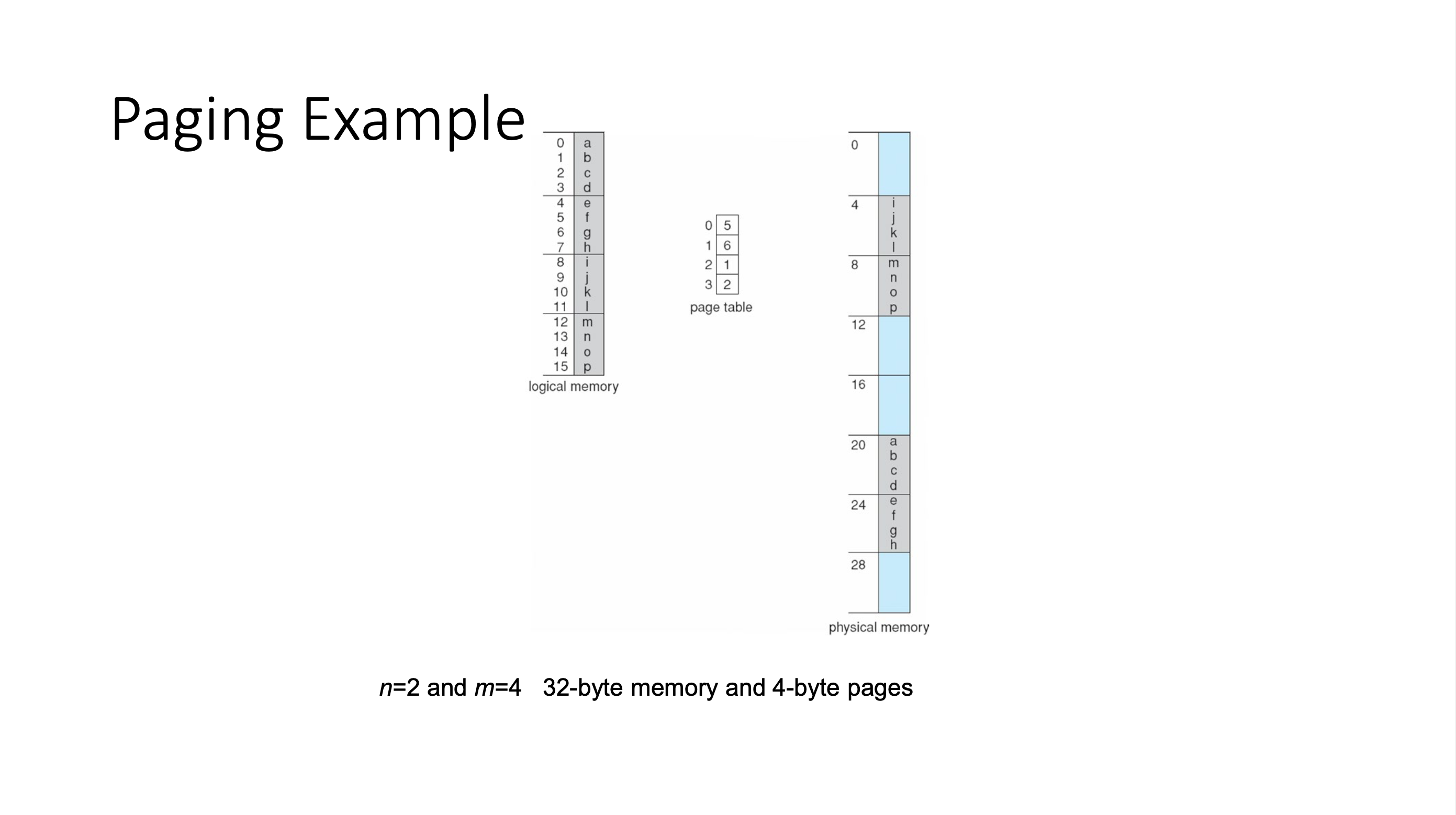

Paging #

- similar to segmentation, except that everything is divided into equal size blocks

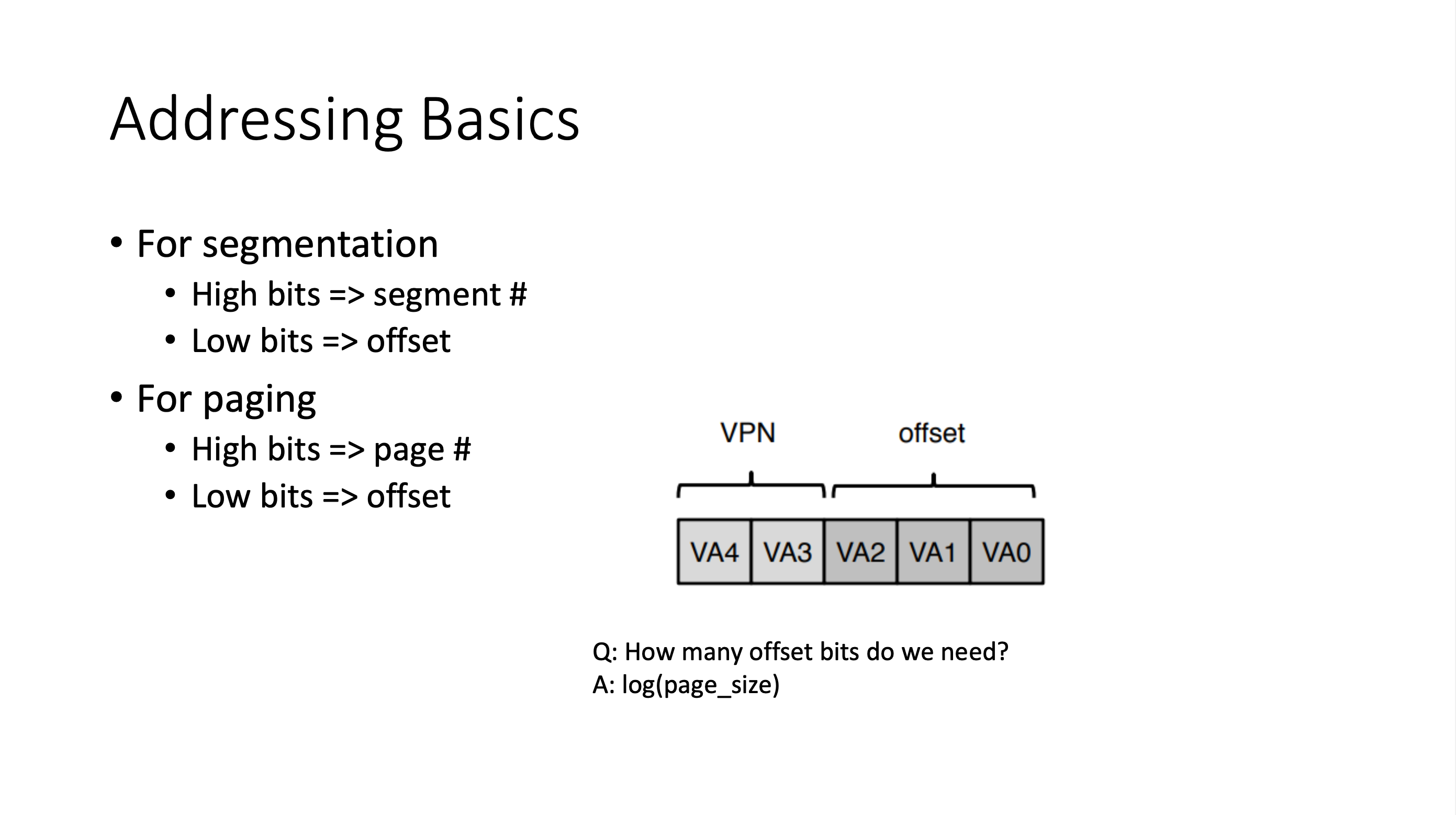

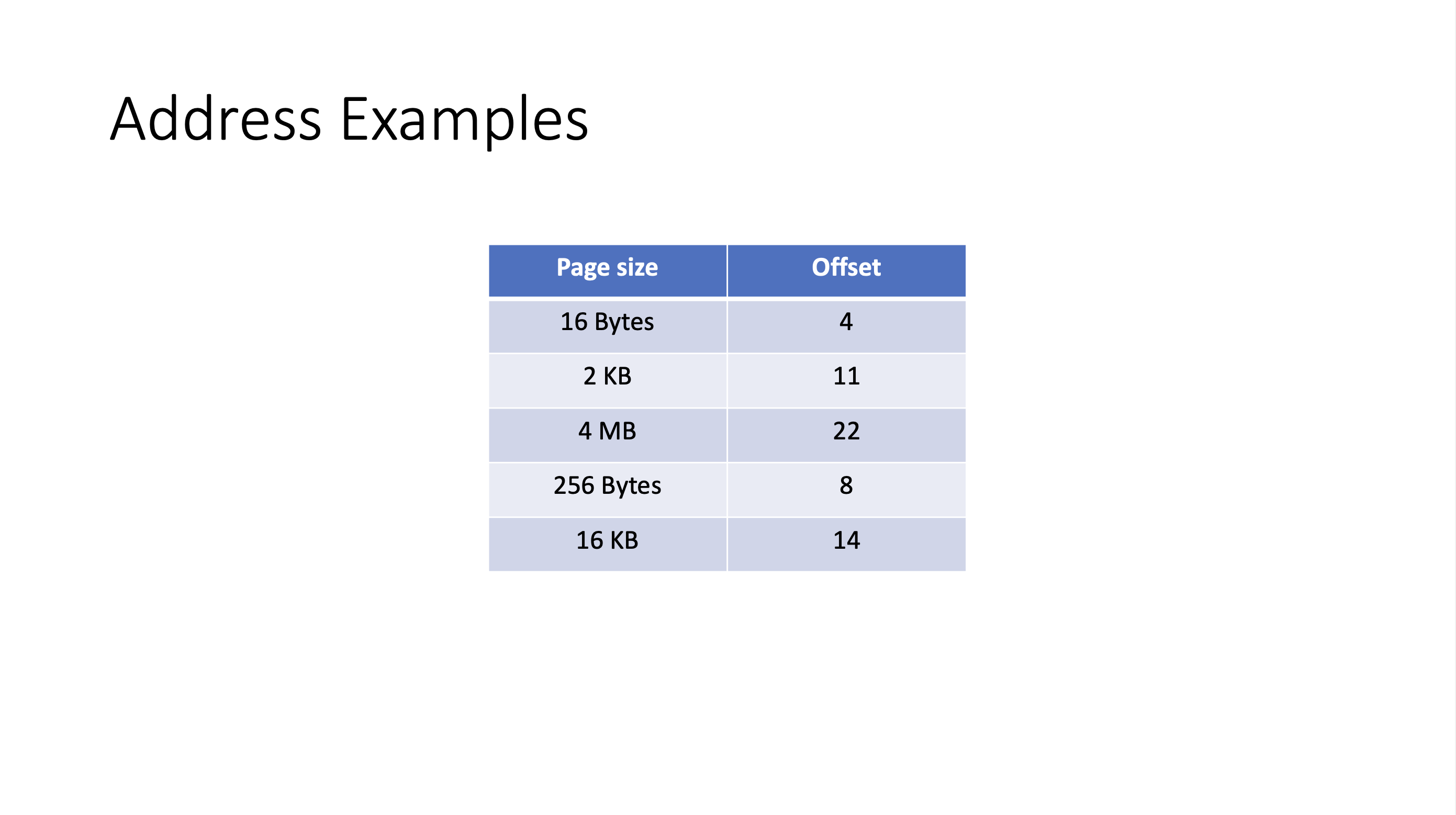

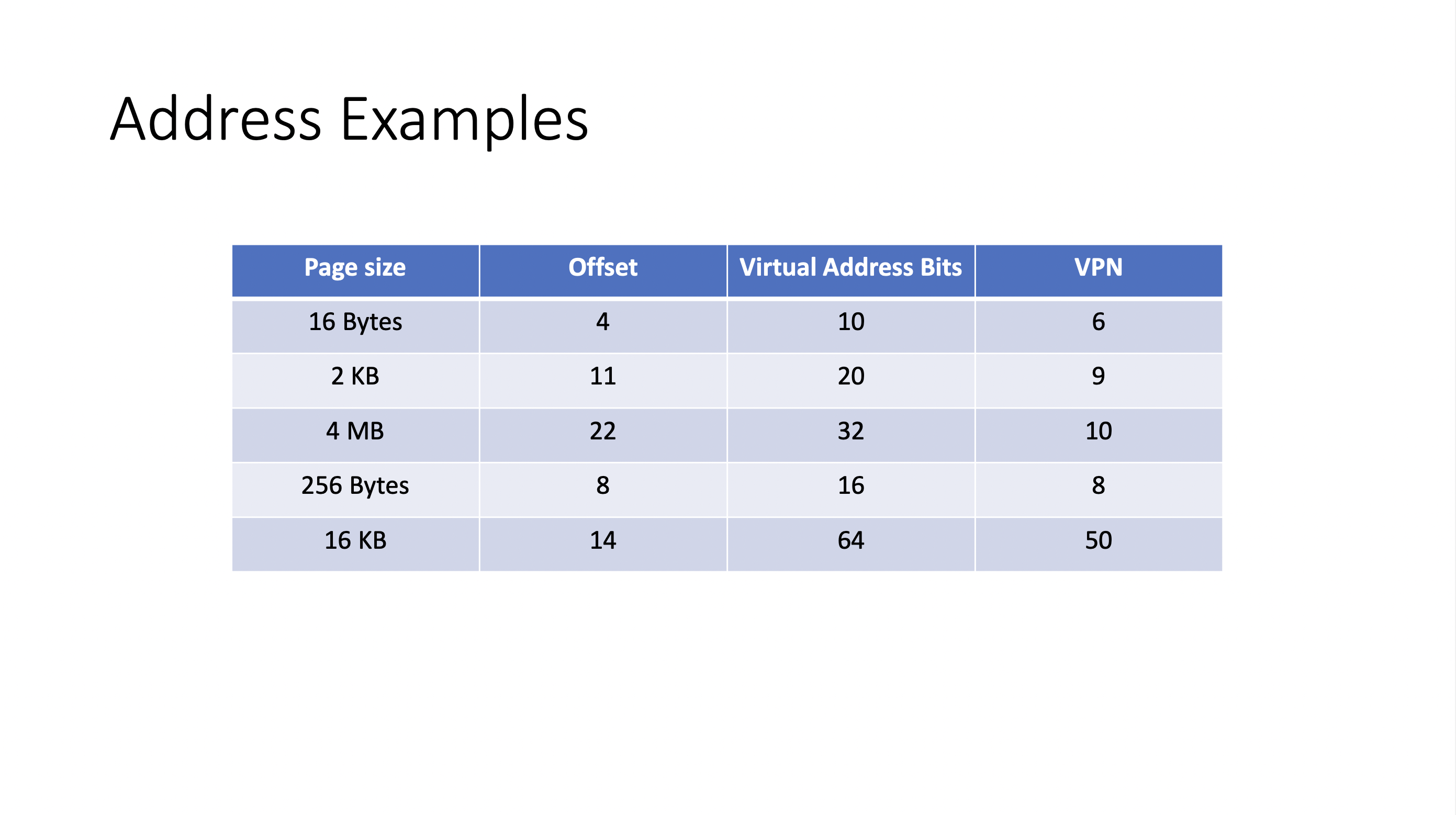

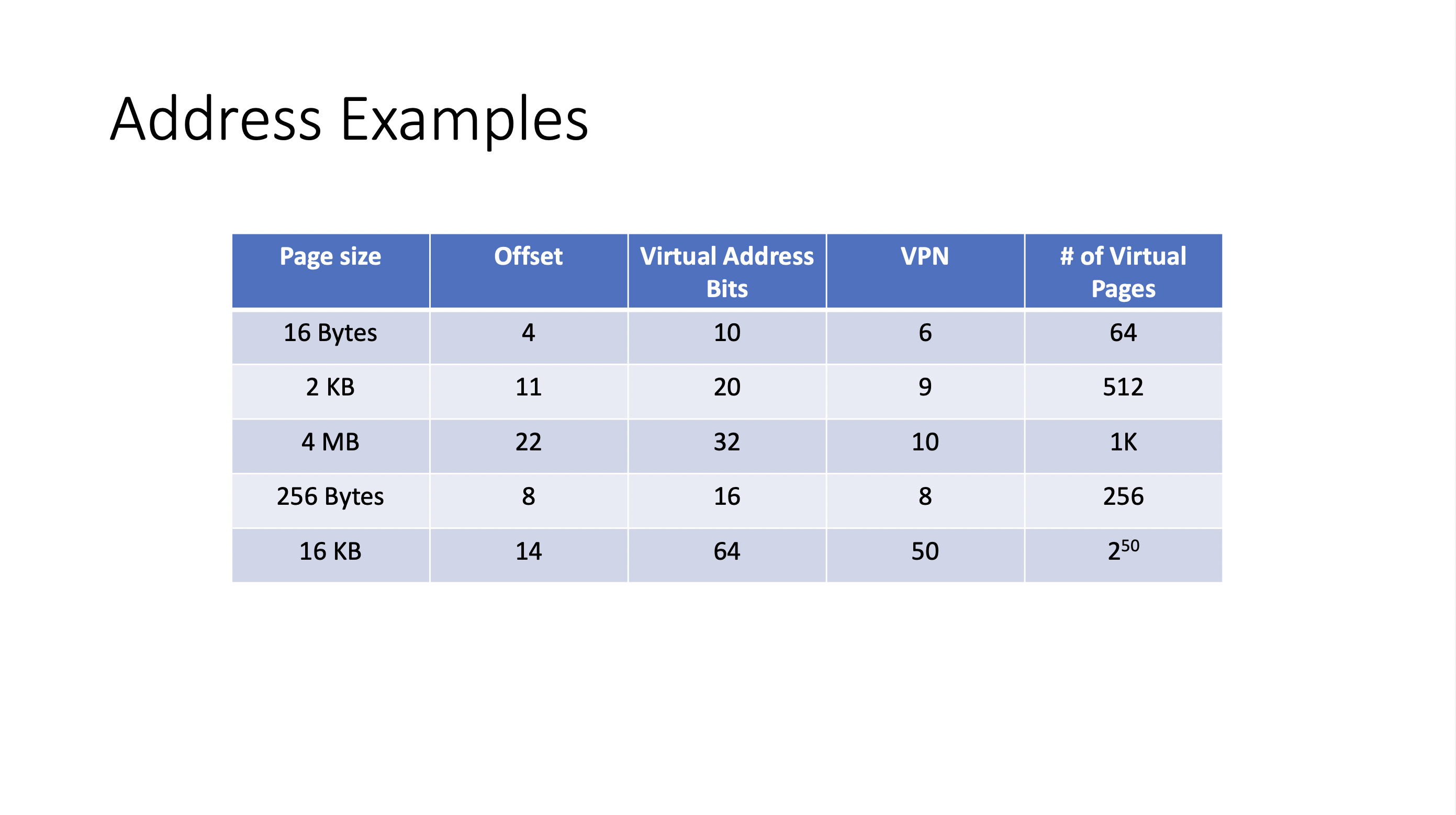

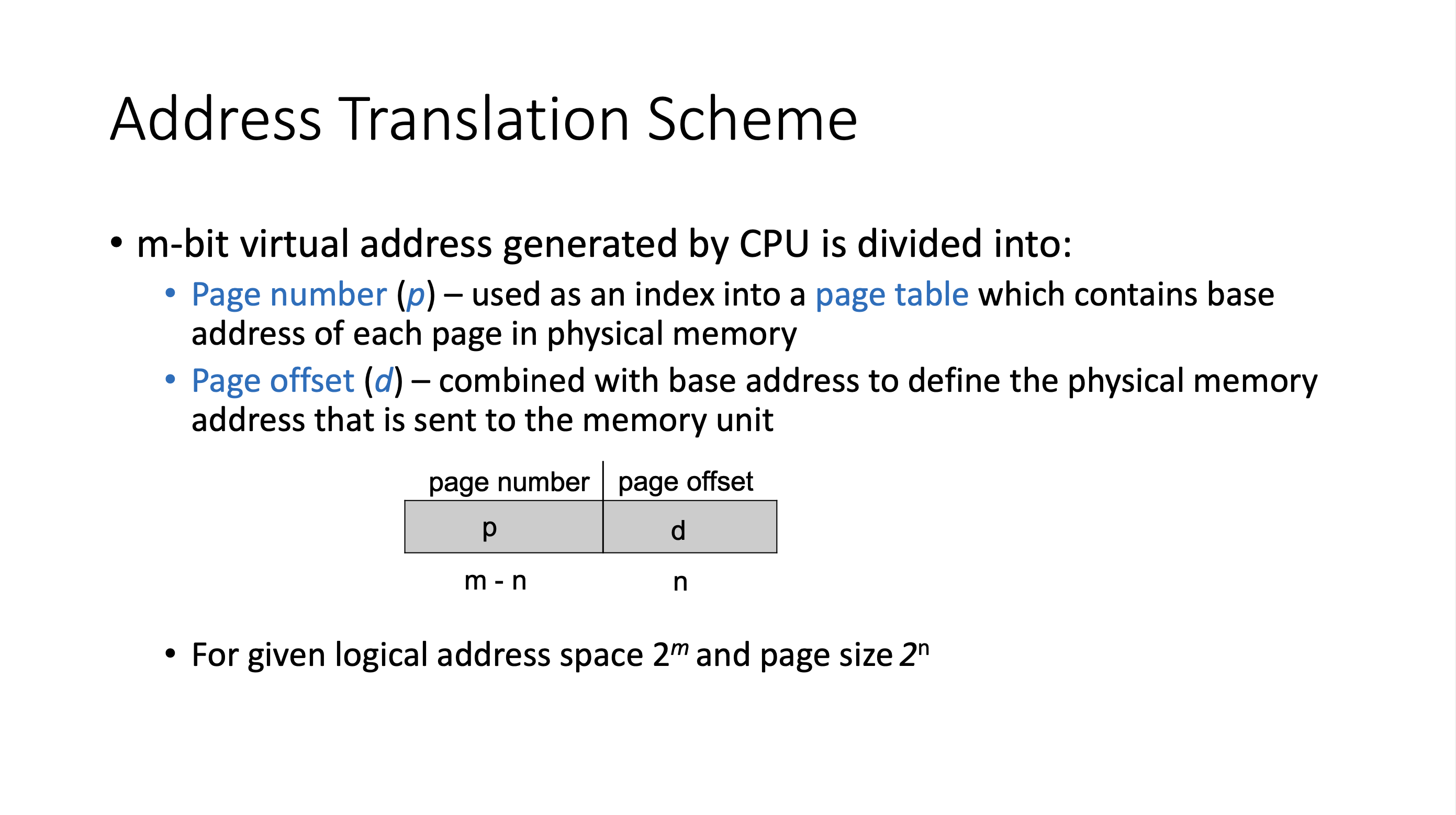

Addressing #

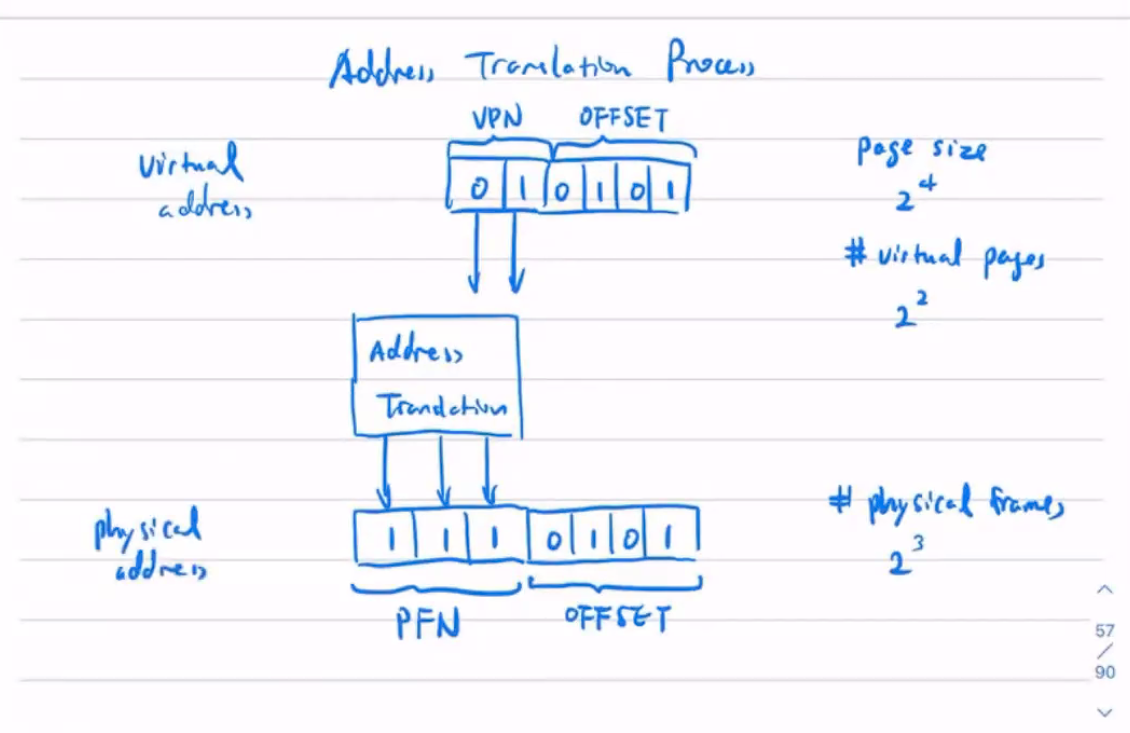

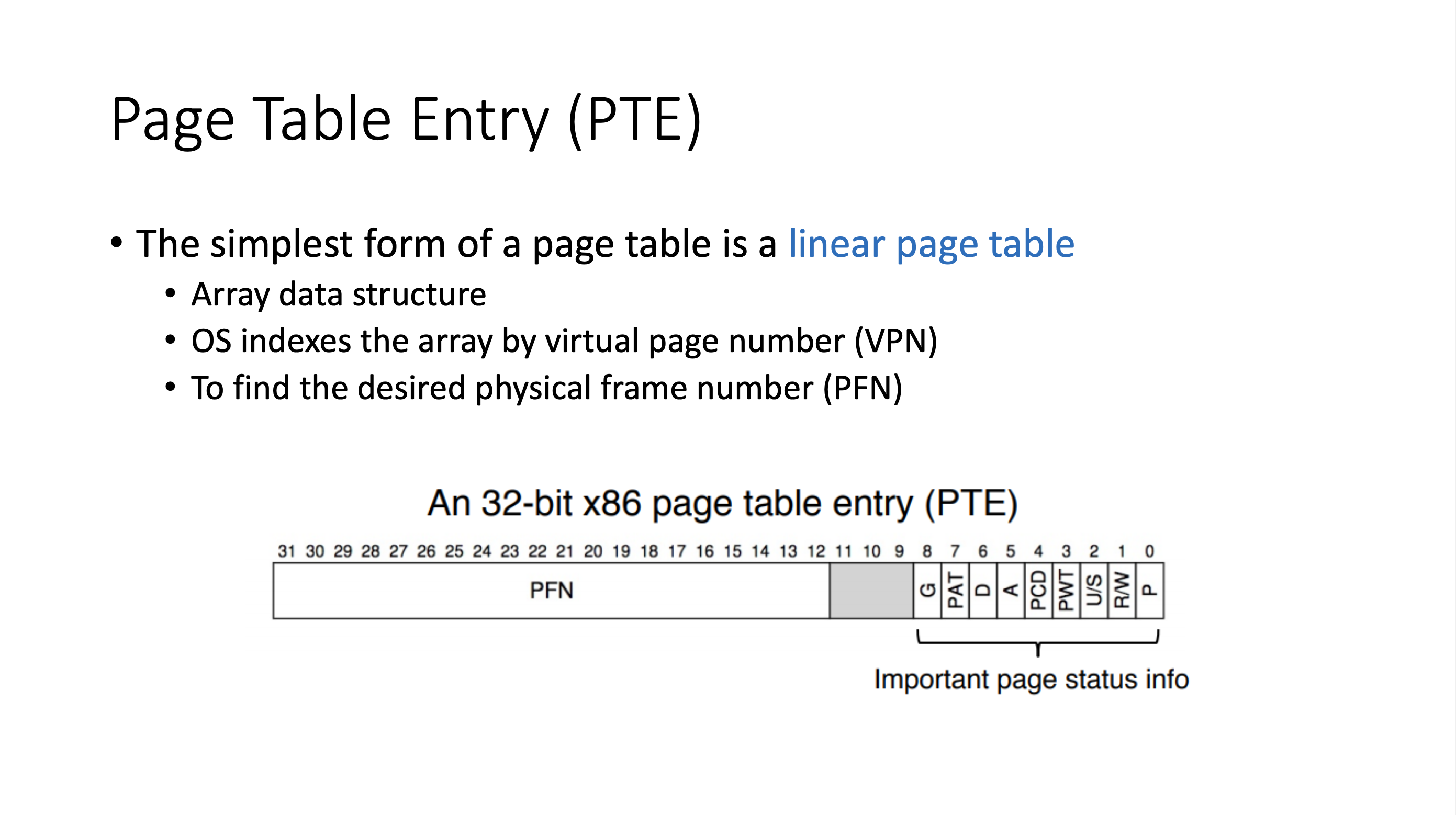

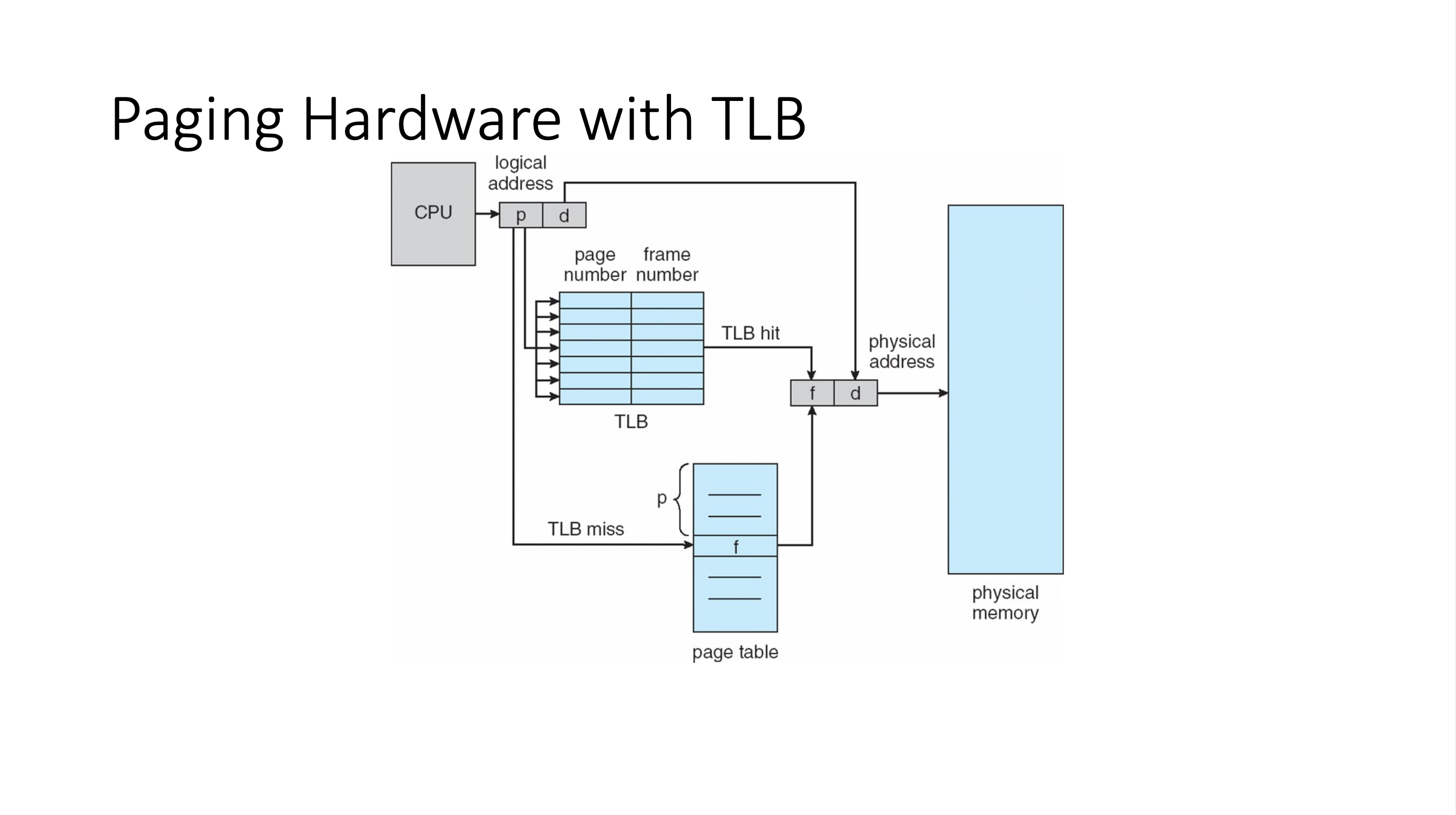

VPN = “virtual page number”, PFN = “physical frame number”

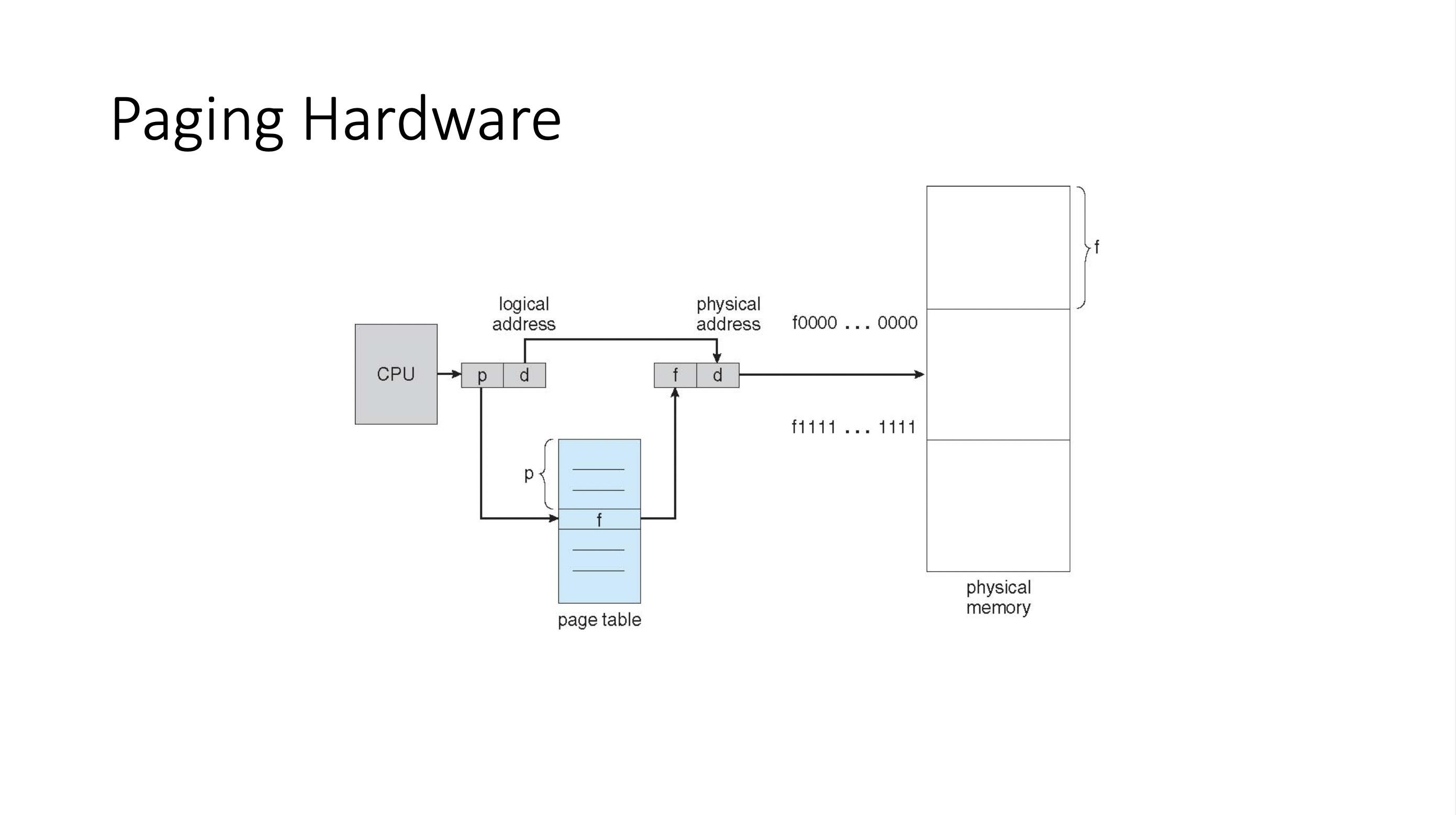

Paging hardware #

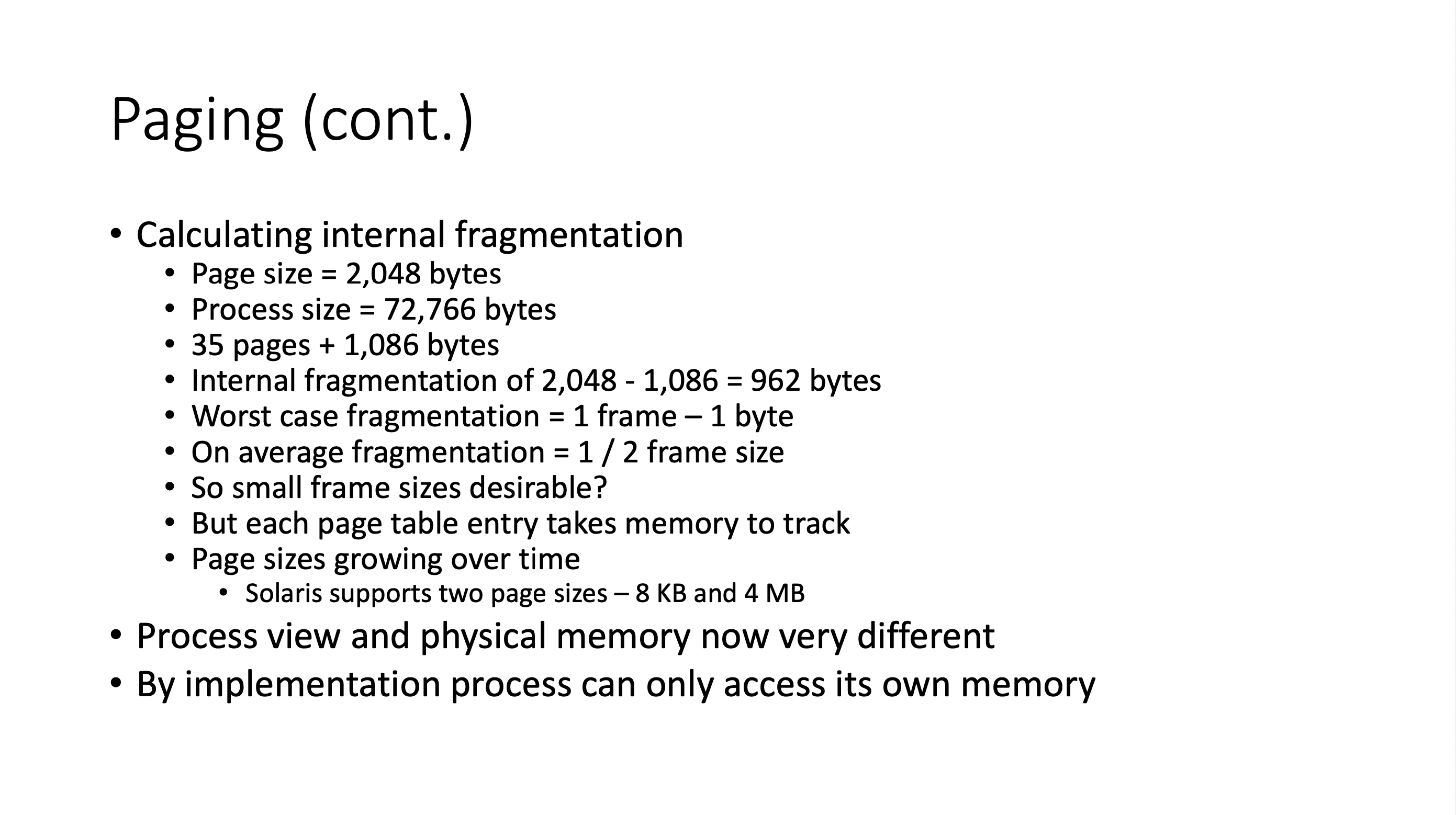

- paging suffers internal fragmentation

- paging solves external fragmentation

Dis the dirty bit, which indicates “write needs to be updated on disk”Ais access bit, indicates if the page has been recently accessedR/Wis protection bit, indicates read or write permissionPis the valid/invalid bit, the “present” bit

Paging problems #

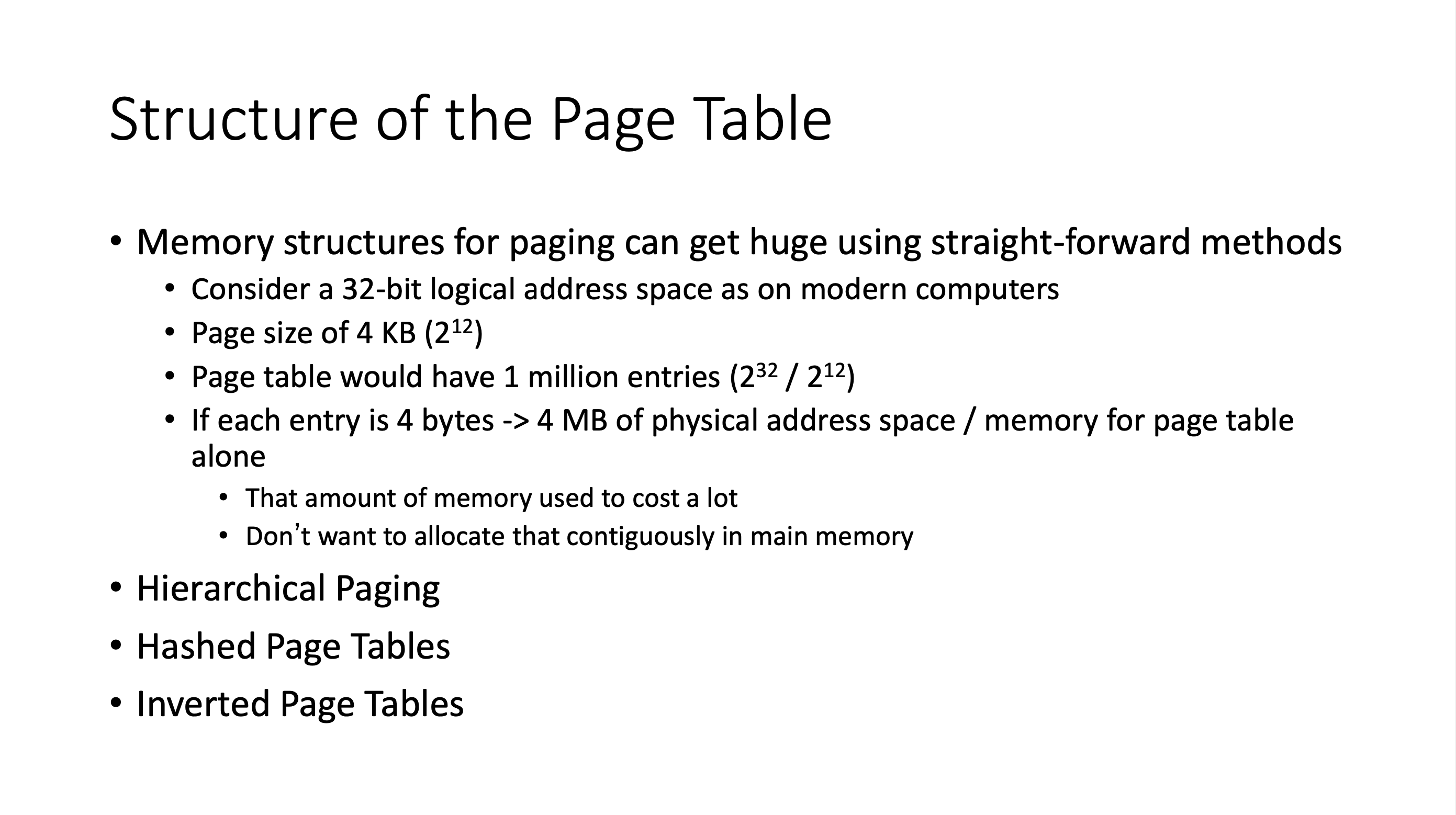

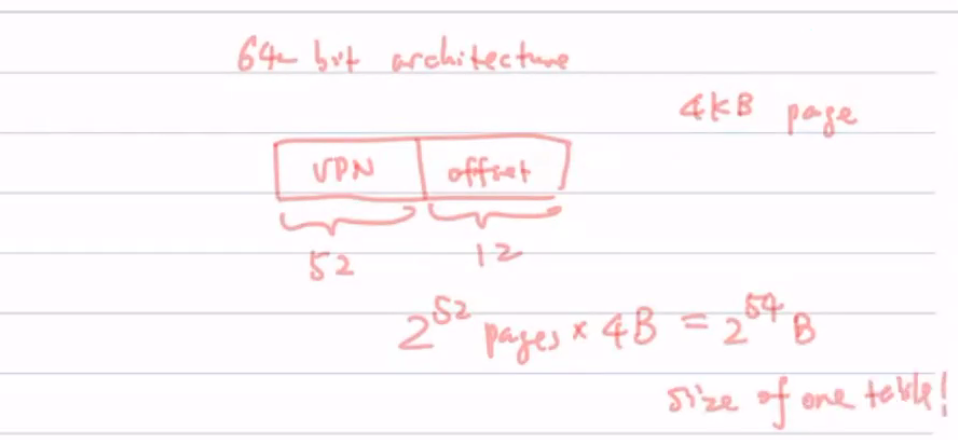

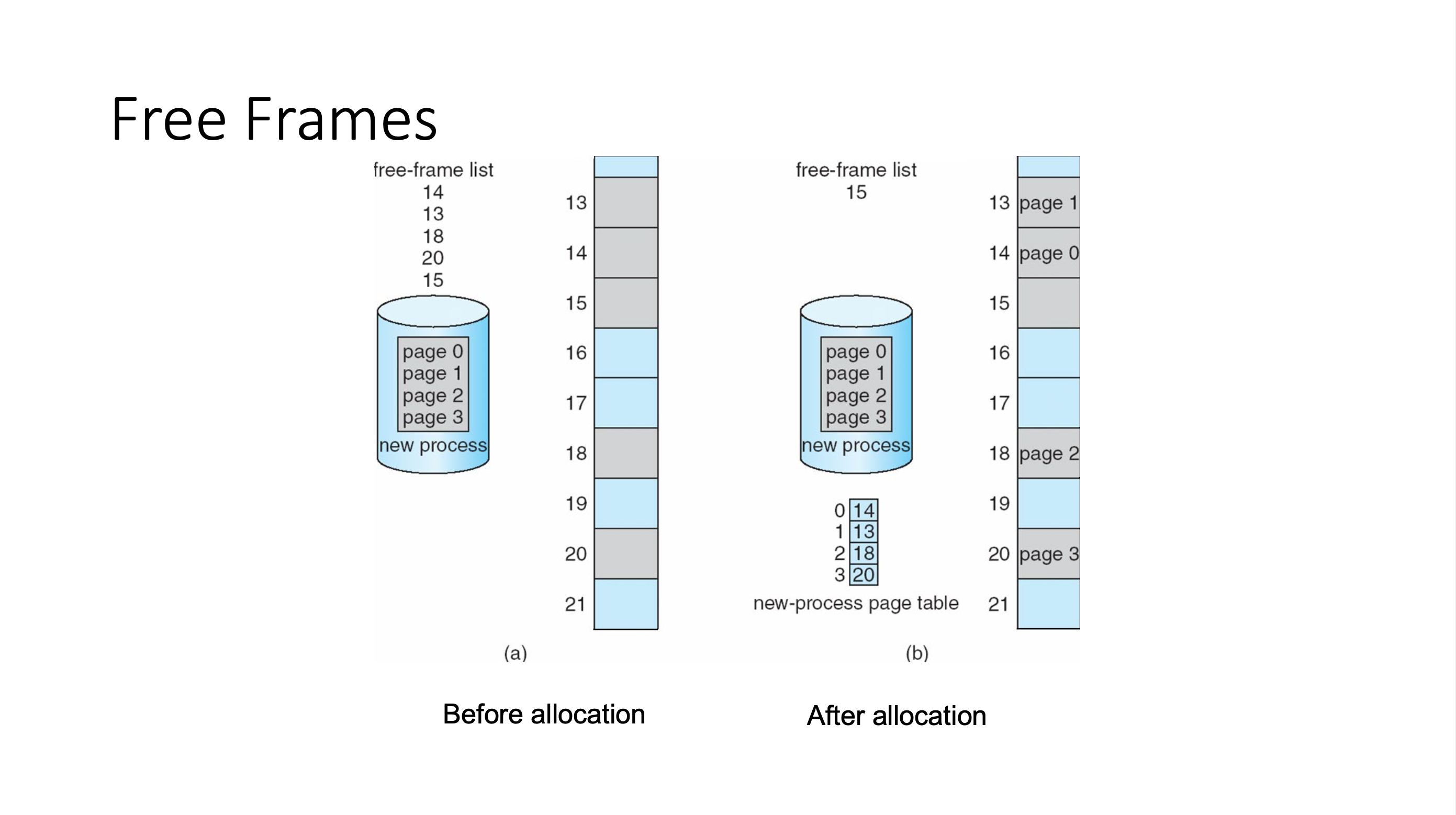

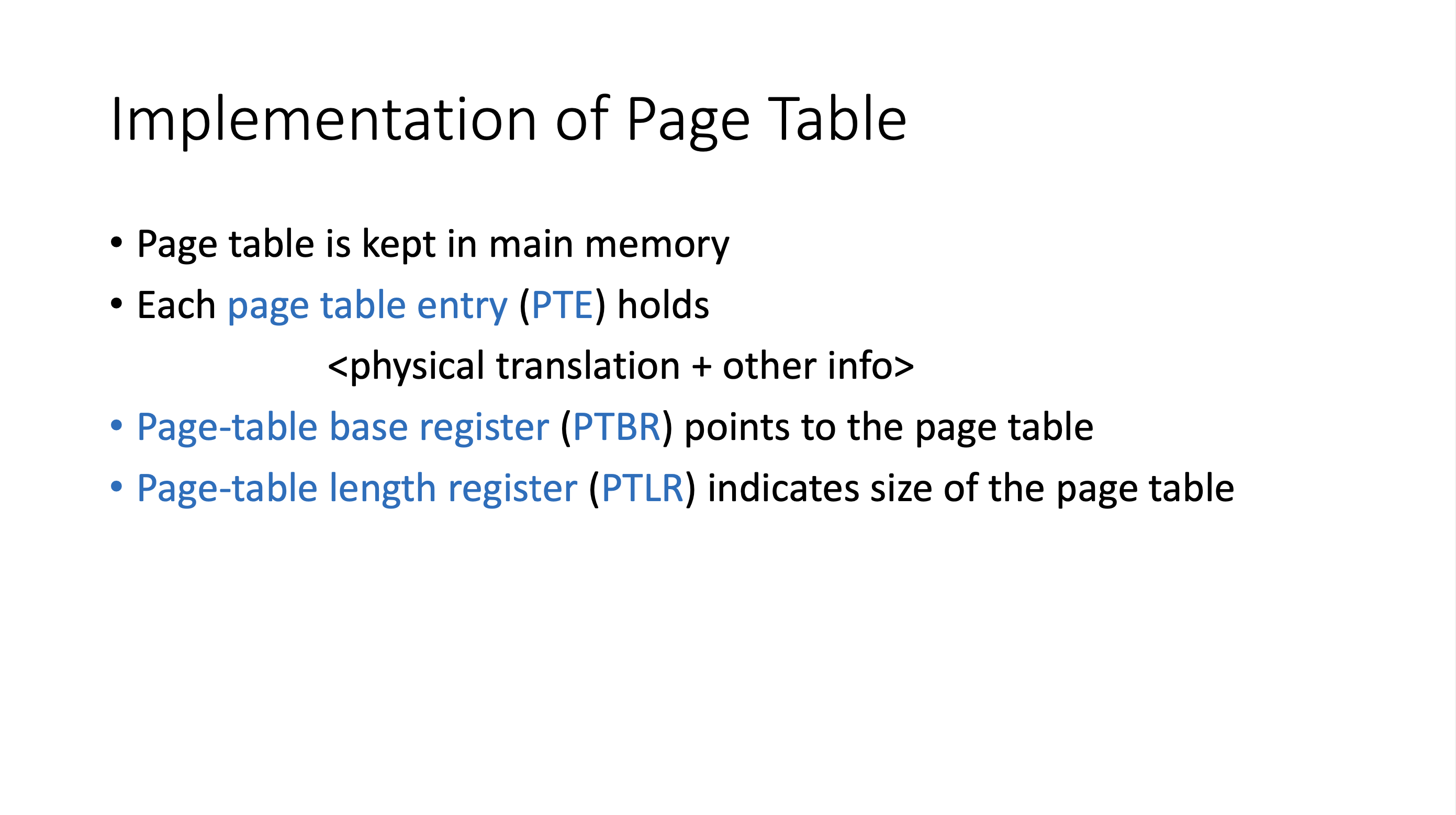

- where do we store the page table itself? in memory

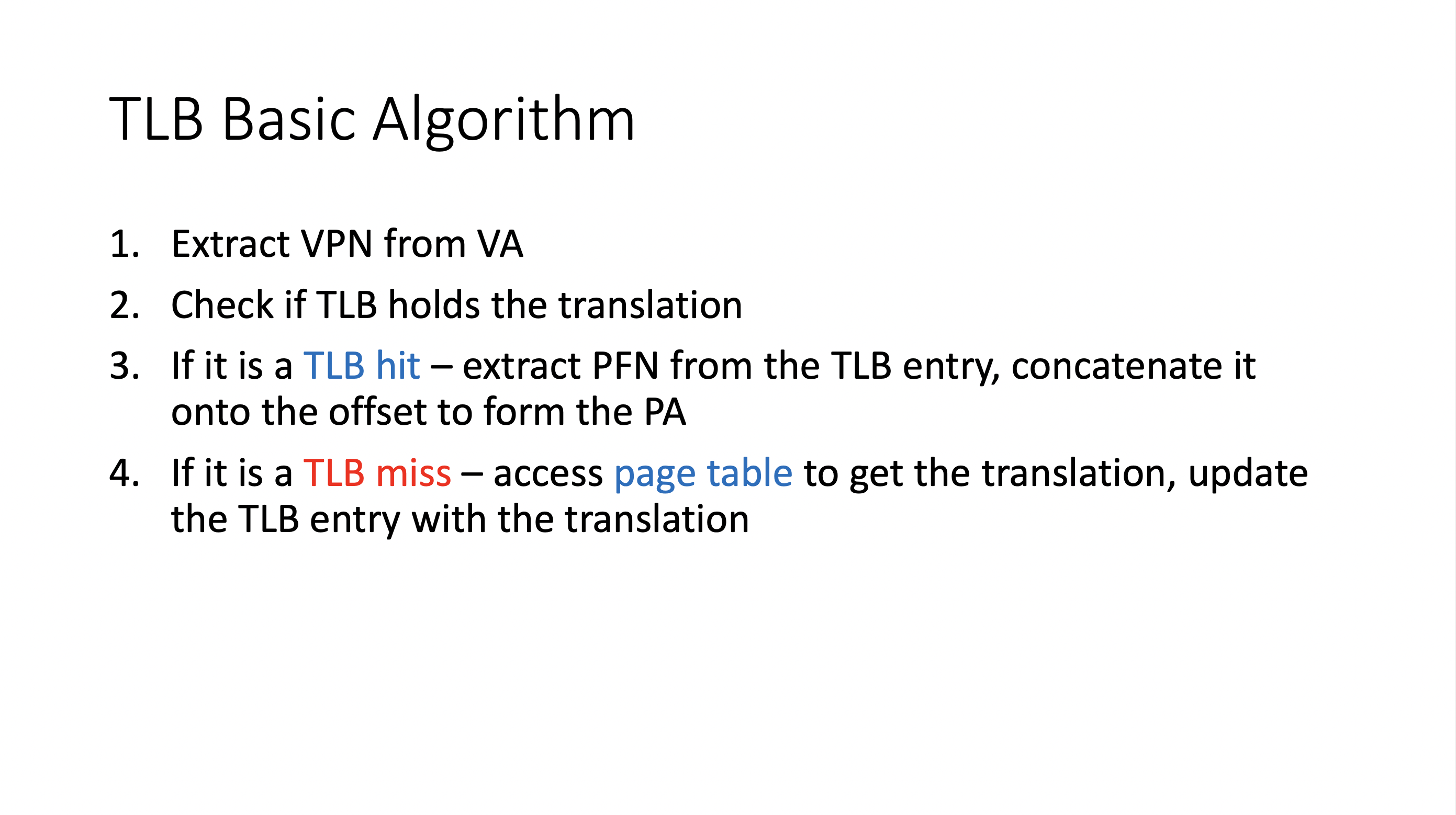

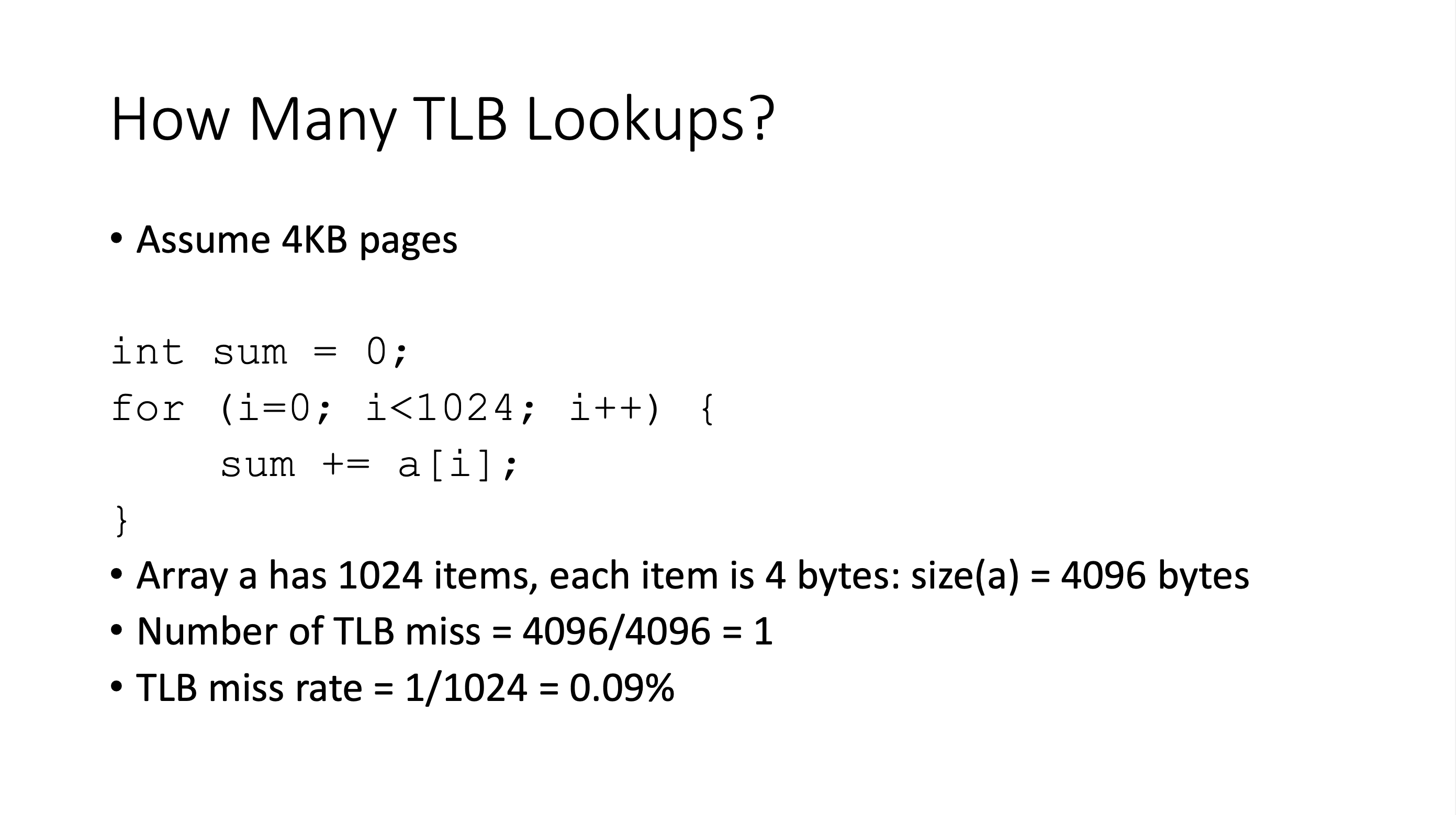

The TLB is the “translation lookaside buffer”. MMU is part of the CPU suite.

TLB Hit

- 1 TLB lookup

- 1 mem access (load/store)

TLB Miss

- 1 TLB lookup (miss)

- 1 mem access(page table lookup)

- 1 TLB update

- 1 mem access (load/store)

We want a high TLB hit rate.

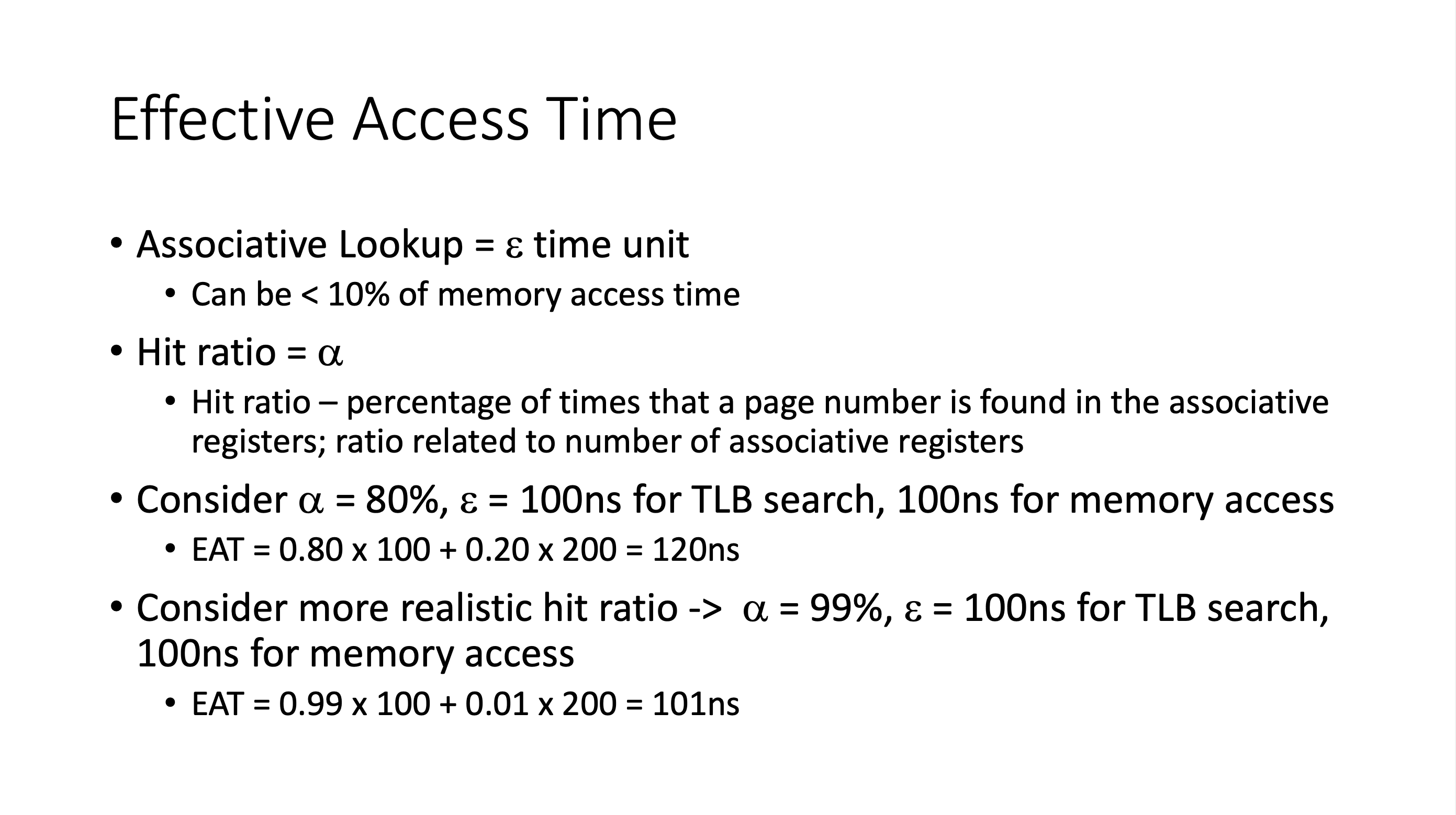

Effective access time #

Structure of a page table #