Propagation delay is the time delta between the input and the output.

Design of a full adder #

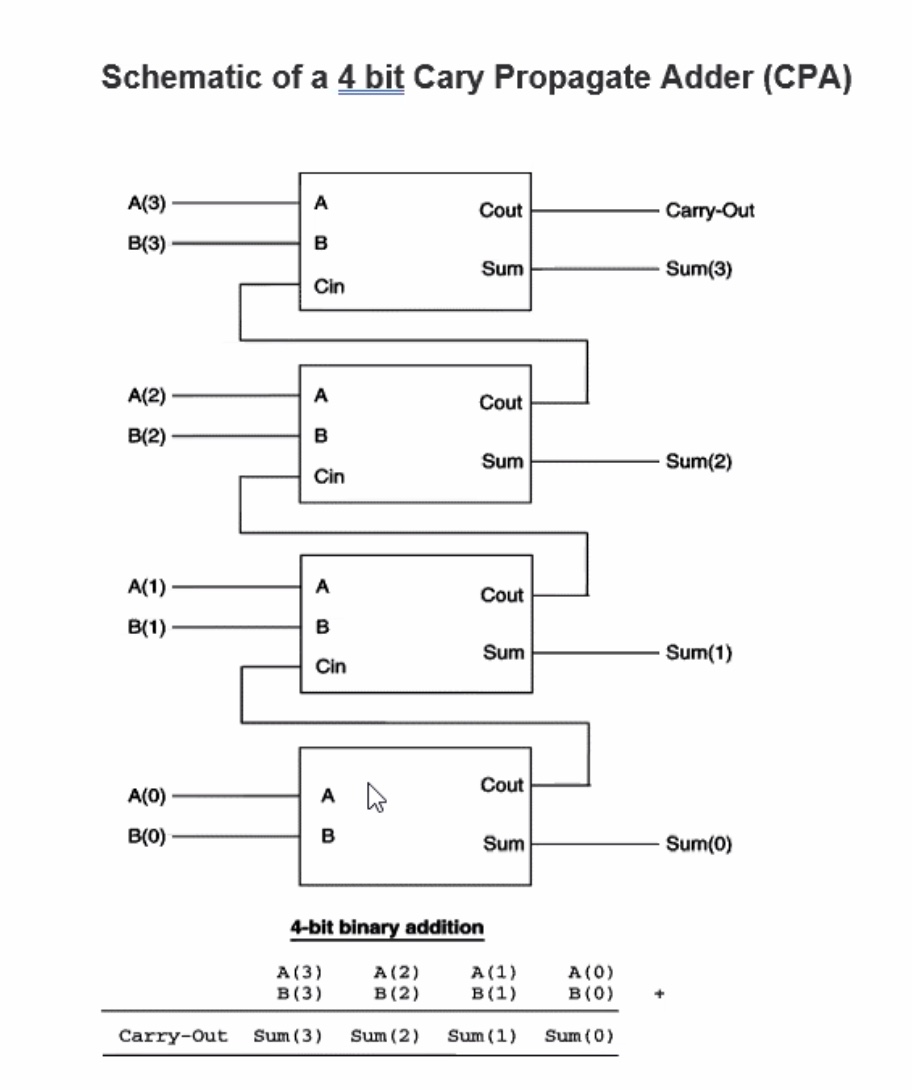

Carry Propagate Adder (CPA)

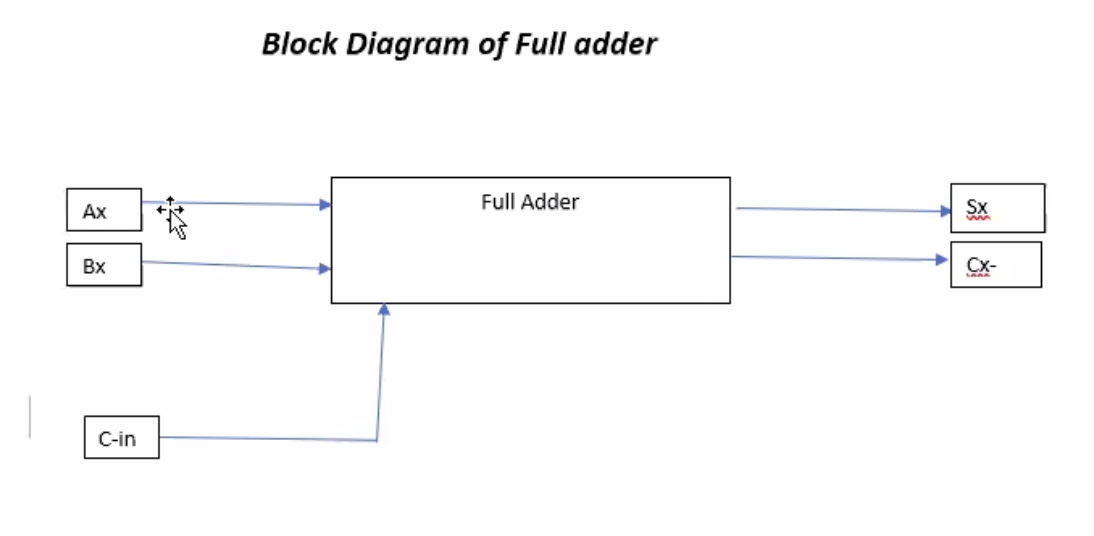

- Full adder is an arithmetic logic unit or circuit to add two single digit numbers with Carry-in

- It is still combinational circuit with inputs

AxandBxSxis the sum (1 bit)C-incarry inCxis the carry out

- Adder is also called Ripple Carry Adder (RCA)

- Fundamental circuit for an adder and has longest propagation delay that is proportional to the number of the carry bits

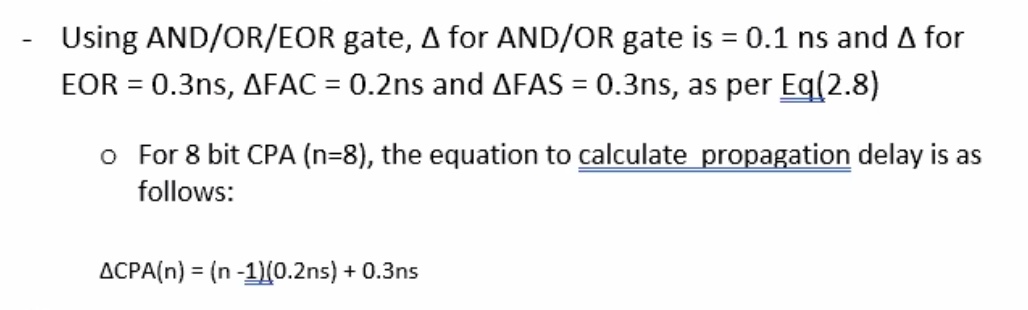

To estimate the propagation delay of an \( n \) -bit CPA:

\[\begin{aligned} \Delta \text{ CPA } (n) = \left[ (n-1) \cdot \Delta FA_C \right] + \Delta FA_S \end{aligned}\]

eg calculating propagation delay #

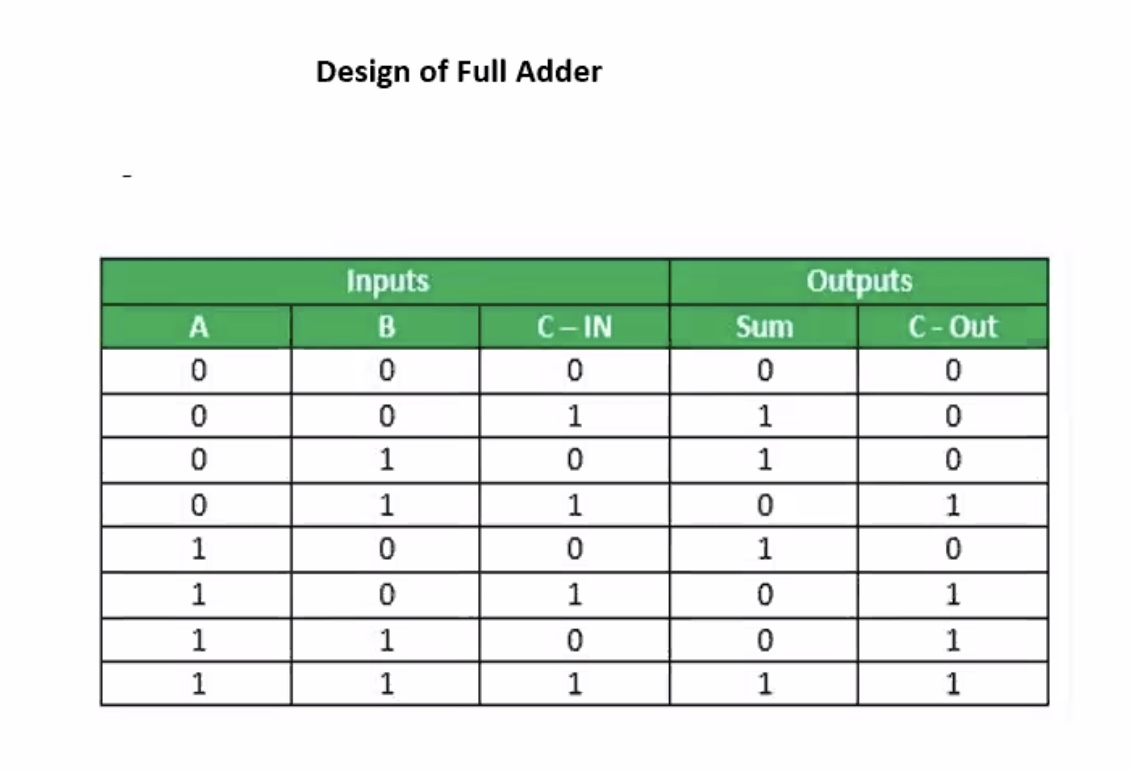

Design of a full adder #

A |

B |

S |

C |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

Lets add

A = 0111

B = 1111

Ai |

Bi |

C-in |

S |

C-out |

|---|---|---|---|---|

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

| 1 | 1 | 1 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |